# Agilent N5413B DDR2(+LP) Compliance Test Application

# **Compliance Testing Notes**

# Notices

© Agilent Technologies, Inc. 2006-2011

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### **Software Version**

Version 01.10.0000

#### Edition

May 2011

Available in electronic format only

Agilent Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

#### **Safety Notices**

#### CAUTION

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# DDR2/LPDDR2 — Quick Reference

Table 1

DDR2/LPDDR2 Cycles and Signals

| TEST                             | Cy           | cle          |              | Base         | d on <sup>·</sup> | Test De      | efinitio     | on                   |            |              |              | nnectio<br>est on |            |                      | Opt. |

|----------------------------------|--------------|--------------|--------------|--------------|-------------------|--------------|--------------|----------------------|------------|--------------|--------------|-------------------|------------|----------------------|------|

|                                  | Read         | Write        | DQ           | DQS          | CK                | ADD          | Ctrl         | Data<br>Mask<br>Ctrl | DQ         | DQS          | CK           | ADD               | Ctrl       | Data<br>Mask<br>Ctrl | CS#  |

| tJIT(per)                        | $\checkmark$ | $\checkmark$ |              |              |                   |              |              |                      |            |              | $\sqrt{1,2}$ |                   |            |                      |      |

| tJIT(cc)                         | $\checkmark$ | $\checkmark$ |              |              |                   |              |              |                      |            |              | $\sqrt{1,2}$ |                   |            |                      |      |

| tERR(nper)                       | $\checkmark$ | $\checkmark$ |              |              |                   |              |              |                      |            |              | $\sqrt{1,2}$ |                   |            |                      |      |

| tCH(avg)                         | $\checkmark$ | $\checkmark$ |              |              |                   |              |              |                      |            |              | $\sqrt{1,2}$ |                   |            |                      |      |

| tCL(avg)                         | $\checkmark$ | $\checkmark$ |              |              |                   |              |              |                      |            |              | √1,2         |                   |            |                      |      |

| tJIT(duty)                       | $\checkmark$ | $\checkmark$ |              |              |                   |              |              |                      |            |              | $\sqrt{1,2}$ |                   |            |                      |      |

| tCK(avg)                         | $\checkmark$ | $\checkmark$ |              |              |                   |              |              |                      |            |              | $\sqrt{1,2}$ |                   |            |                      |      |

| rERR(13–50p<br>er)(Low<br>Power) | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$      |              |              |                      |            |              | √1,2         |                   |            |                      |      |

| tCH(abs)                         | $\checkmark$ | $\checkmark$ |              |              |                   |              |              |                      |            |              | $\sqrt{1,2}$ |                   |            |                      |      |

| tCL(abs)                         | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$      |              |              |                      |            |              | √1,2         |                   |            |                      |      |

| tCK(abs)                         | $\checkmark$ | $\checkmark$ |              |              |                   |              |              |                      |            |              | $\sqrt{1,2}$ |                   |            |                      |      |

| V <sub>IH(AC)</sub>              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$      |              |              |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1}$   | $\sqrt{1}$        | $\sqrt{1}$ | $\sqrt{1}$           |      |

| V <sub>IH(DC)</sub>              |              | $\checkmark$ | $\checkmark$ |              |                   | $\checkmark$ |              |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1}$   | $\sqrt{1}$        | $\sqrt{1}$ | $\sqrt{1}$           |      |

| V <sub>IL(AC)</sub>              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |                   | $\checkmark$ |              |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1}$   | $\sqrt{1}$        | $\sqrt{1}$ | $\sqrt{1}$           |      |

| V <sub>IL(DC)</sub>              |              | $\checkmark$ | $\checkmark$ |              |                   | $\checkmark$ |              |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1}$   | $\sqrt{1}$        | $\sqrt{1}$ | $\sqrt{1}$           |      |

| Slew <sub>R</sub>                |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |                   | $\checkmark$ |              |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1}$   | $\sqrt{1}$        | $\sqrt{1}$ | $\sqrt{1}$           |      |

| Slew <sub>F</sub>                |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |                   | $\checkmark$ | $\checkmark$ |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1}$   | $\sqrt{1}$        | $\sqrt{1}$ | $\sqrt{1}$           |      |

| AC<br>Overshoot                  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$      | $\checkmark$ | $\checkmark$ | $\checkmark$         | $\sqrt{1}$ | $\sqrt{1}$   | $\sqrt{1}$   | $\sqrt{1}$        | $\sqrt{1}$ | $\sqrt{1}$           |      |

| AC<br>Undershoot                 | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$      | $\checkmark$ | $\checkmark$ |                      | $\sqrt{1}$ | $\sqrt{1}$   | $\sqrt{1}$   | $\sqrt{1}$        | $\sqrt{1}$ | $\sqrt{1}$           |      |

| V <sub>IHCA(AC)</sub>            |              | $\checkmark$ |              |              |                   |              | $\checkmark$ |                      |            |              |              | $\sqrt{1}$        | $\sqrt{1}$ |                      |      |

| V <sub>ILCA(AC)</sub>            |              | $\checkmark$ |              |              |                   |              |              |                      |            |              |              | $\sqrt{1}$        | $\sqrt{1}$ |                      |      |

NOTE: 1 = Single Ended signal; 2 = Differential signal; 3 = 2 x Single Ended signal

| TEST                                  | Cycle        |              |              | Base         | d on ' | Test De | efiniti | on                   | R          | equire       | d to P     | erform     | on So      | ope                  | Opt. |

|---------------------------------------|--------------|--------------|--------------|--------------|--------|---------|---------|----------------------|------------|--------------|------------|------------|------------|----------------------|------|

|                                       | Read         | Write        | DQ           | DQS          | CK     | ADD     | Ctrl    | Data<br>Mask<br>Ctrl | DQ         | DQS          | CK         | ADD        | Ctrl       | Data<br>Mask<br>Ctrl | CS#  |

| V <sub>IHCA(DC)</sub>                 |              | $\checkmark$ |              |              |        |         |         |                      |            |              |            | $\sqrt{1}$ | $\sqrt{1}$ |                      |      |

| V <sub>ILCA(DC)</sub>                 |              | $\checkmark$ |              |              |        |         |         |                      |            |              |            | $\sqrt{1}$ | $\sqrt{1}$ |                      |      |

| V <sub>IHDQ(AC)</sub>                 |              | $\checkmark$ | $\checkmark$ |              |        |         |         | $\checkmark$         | $\sqrt{1}$ | $\sqrt{1,2}$ |            |            |            | $\sqrt{1}$           |      |

| V <sub>ILDQ(AC)</sub>                 |              | $\checkmark$ | $\checkmark$ |              |        |         |         | $\checkmark$         | $\sqrt{1}$ | $\sqrt{1,2}$ |            |            |            | $\sqrt{1}$           |      |

| V <sub>IHDQ(DC)</sub>                 |              | $\checkmark$ | $\checkmark$ |              |        |         |         | $\checkmark$         | $\sqrt{1}$ | $\sqrt{1,2}$ |            |            |            | $\sqrt{1}$           |      |

| V <sub>ILDQ(DC)</sub>                 |              | $\checkmark$ | $\checkmark$ |              |        |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |            |            |            | $\sqrt{1}$           |      |

| SRQseR<br>(RON = 40<br>ohm +/- 30%)   | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |        |         |         |                      | $\sqrt{1}$ | √1,2         |            |            |            |                      |      |

| SRQseF<br>(RON = 40<br>ohm +/- 30%)   | V            |              | $\checkmark$ | $\checkmark$ |        |         |         |                      | $\sqrt{1}$ | √1,2         |            |            |            |                      |      |

| SRQseR<br>(RON = 60<br>ohm +/- 30%)   | V            |              | $\checkmark$ | $\checkmark$ |        |         |         |                      | $\sqrt{1}$ | √1,2         |            |            |            |                      |      |

| SRQseF<br>(RON = 60<br>ohm +/- 30%)   | V            |              | $\checkmark$ | $\checkmark$ |        |         |         |                      | $\sqrt{1}$ | √1,2         |            |            |            |                      |      |

| V <sub>OH(AC)</sub>                   | $\checkmark$ |              | $\checkmark$ |              |        |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |            |            |            |                      |      |

| V <sub>OH(DC)</sub>                   | $\checkmark$ |              | $\checkmark$ |              |        |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |            |            |            |                      |      |

| V <sub>OL(AC)</sub>                   | $\checkmark$ |              | $\checkmark$ |              |        |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |            |            |            |                      |      |

| V <sub>OL(DC)</sub>                   | $\checkmark$ |              |              | $\checkmark$ |        |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |            |            |            |                      |      |

| V <sub>SEH(AC)</sub> , for<br>strobes |              | $\checkmark$ |              | $\checkmark$ |        |         |         |                      | $\sqrt{1}$ | $\sqrt{1}$   |            |            |            |                      |      |

| V <sub>SEL(AC)</sub> , for<br>strobes |              | $\checkmark$ |              | $\checkmark$ |        |         |         |                      | $\sqrt{1}$ | $\sqrt{1}$   |            |            |            |                      |      |

| V <sub>SEH(AC)</sub> , for<br>clocks  | $\checkmark$ | $\checkmark$ |              |              |        |         |         |                      |            |              | $\sqrt{1}$ |            |            |                      |      |

NOTE: 1 = Single Ended signal; 2 = Differential signal;  $3 = 2 \times Single$  Ended signal

| TEST                                  | Cy           | cle          | Based on Test Definition |              |              |     |      |                      |            | equire       | d to P     | erform | on Sc | ope                  | Opt.         |

|---------------------------------------|--------------|--------------|--------------------------|--------------|--------------|-----|------|----------------------|------------|--------------|------------|--------|-------|----------------------|--------------|

|                                       | Read         | Write        | DQ                       | DQS          | CK           | ADD | Ctrl | Data<br>Mask<br>Ctrl | DQ         | DQS          | CK         | ADD    | Ctrl  | Data<br>Mask<br>Ctrl | CS#          |

| V <sub>SEL(AC)</sub> , for<br>clocks  | V            | $\checkmark$ |                          |              | $\checkmark$ |     |      |                      |            |              | $\sqrt{1}$ |        |       |                      |              |

| V <sub>ID(AC)</sub>                   |              | $\checkmark$ |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{3}$   | $\sqrt{3}$ |        |       |                      |              |

| V <sub>IX(AC)</sub>                   |              | $\checkmark$ |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{3}$   | $\sqrt{3}$ |        |       |                      |              |

| V <sub>OX(AC)</sub>                   | $\checkmark$ |              |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{3}$   |            |        |       |                      |              |

| V <sub>IXCA</sub>                     | $\checkmark$ | $\checkmark$ |                          |              |              |     |      |                      |            |              | $\sqrt{3}$ |        |       |                      |              |

| V <sub>IXDQ</sub>                     |              | $\checkmark$ |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{3}$   |            |        |       |                      |              |

| V <sub>IHdiff(DC)</sub>               |              | $\checkmark$ |                          | $\checkmark$ | $\checkmark$ |     |      |                      | $\sqrt{1}$ | $\sqrt{2}$   | $\sqrt{2}$ |        |       |                      |              |

| V <sub>ILdiff(DC)</sub>               |              | $\checkmark$ |                          | $\checkmark$ | $\checkmark$ |     |      |                      | $\sqrt{1}$ | $\sqrt{2}$   | $\sqrt{2}$ |        |       |                      |              |

| V <sub>IHdiff(AC)</sub>               |              | $\checkmark$ |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{2}$   | $\sqrt{2}$ |        |       |                      |              |

| V <sub>ILdiff(AC)</sub>               |              | $\checkmark$ |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{2}$   | $\sqrt{2}$ |        |       |                      |              |

| SRQdiffR<br>(RON = 40<br>ohm +/- 30%) | $\checkmark$ |              |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{2}$   |            |        |       |                      |              |

| SRQdiffF<br>(RON = 40<br>ohm +/- 30%) | $\checkmark$ |              |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{2}$   |            |        |       |                      |              |

| SRQdiffR<br>(RON = 60<br>ohm +/- 30%) | $\checkmark$ |              |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{2}$   |            |        |       |                      |              |

| SRQdiffF<br>(RON = 60<br>ohm +/- 30%) | $\checkmark$ |              |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{2}$   |            |        |       |                      |              |

| V <sub>OHdiff(AC)</sub>               | $\checkmark$ |              |                          |              |              |     |      |                      | $\sqrt{1}$ | $\sqrt{2}$   |            |        |       |                      |              |

| V <sub>OLdiff(AC)</sub>               | $\checkmark$ |              |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{2}$   |            |        |       |                      |              |

| tAC                                   | $\checkmark$ |              | $\checkmark$             |              |              |     |      |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | √1,2       |        |       |                      | $\checkmark$ |

| tDQSCK                                | $\checkmark$ |              |                          | $\checkmark$ |              |     |      |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | √1,2       |        |       |                      | $\checkmark$ |

| tDQSCK<br>(Low Power)                 | $\checkmark$ |              |                          | $\checkmark$ | $\checkmark$ |     |      |                      | $\sqrt{1}$ | √1,2         | √1,2       |        |       |                      | $\checkmark$ |

NOTE: 1 = Single Ended signal; 2 = Differential signal; 3 = 2 x Single Ended signal

| TEST                  | Cy           | vcle         |              | Base         | d on '       | Test De | efiniti | on                   | R          | lequire      | d to P       | erform | on Sc | ope                  | Opt.         |

|-----------------------|--------------|--------------|--------------|--------------|--------------|---------|---------|----------------------|------------|--------------|--------------|--------|-------|----------------------|--------------|

|                       | Read         | Write        | DQ.          | DQS          | СК           | ADD     | Ctrl    | Data<br>Mask<br>Ctrl | DQ         | DQS          | CK           | ADD    | Ctrl  | Data<br>Mask<br>Ctrl | CS#          |

| tDVAC<br>(Clock)      | $\checkmark$ | $\checkmark$ |              |              |              |         |         |                      |            |              | $\sqrt{2}$   |        |       |                      |              |

| tQHS                  | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |         |         |                      | $\sqrt{1}$ | √1,2         | √1,2         |        |       |                      | $\checkmark$ |

| tHZ(DQ)               | $\checkmark$ |              | $\checkmark$ |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1,2}$ |        |       |                      | $\checkmark$ |

| tLZ(DQS)              | $\checkmark$ |              |              |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1,2}$ |        |       |                      | $\checkmark$ |

| tLZ(DQ)               | $\checkmark$ |              | $\checkmark$ |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1,2}$ |        |       |                      | $\checkmark$ |

| tDQSQ                 | $\checkmark$ |              | $\checkmark$ |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |              |        |       |                      |              |

| tΩH                   | $\checkmark$ |              | $\checkmark$ |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |              |        |       |                      |              |

| tDQSS                 |              | $\checkmark$ |              |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1,2}$ |        |       |                      |              |

| tDQSH                 |              | $\checkmark$ |              |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |              |        |       |                      | $\checkmark$ |

| tDQSL                 |              | $\checkmark$ |              |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |              |        |       |                      | $\checkmark$ |

| tDSS                  |              | $\checkmark$ |              |              | $\checkmark$ |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | √1,2         |        |       |                      | $\checkmark$ |

| tDSH                  |              |              |              |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ | $\sqrt{1,2}$ |        |       |                      |              |

| tWPST                 |              |              |              |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |              |        |       |                      |              |

| tWPRE                 |              |              |              |              |              |         |         |                      | $\sqrt{1}$ | √1,2         |              |        |       |                      |              |

| tRPRE                 | $\checkmark$ |              |              |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |              |        |       |                      |              |

| tRPST                 | $\checkmark$ |              |              |              |              |         |         |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |              |        |       |                      |              |

| tHZ(DQ) Low<br>Power  | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |         |         |                      | $\sqrt{1}$ | √1,2         | √1,2         |        |       |                      | $\checkmark$ |

| tHZ(DQS)<br>Low Power | $\checkmark$ |              |              | $\checkmark$ |              |         |         |                      | $\sqrt{1}$ | √1,2         | √1,2         |        |       |                      | $\checkmark$ |

| tLZ(DQ) Low<br>Power  | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |         |         |                      | $\sqrt{1}$ | √1,2         | √1,2         |        |       |                      | $\checkmark$ |

| tLZ(DQS)<br>Low Power | $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ |         |         |                      | $\sqrt{1}$ | √1,2         | √1,2         |        |       |                      | $\checkmark$ |

| tQSH                  | $\checkmark$ |              |              |              |              |         |         |                      | $\sqrt{1}$ | √1,2         |              |        |       |                      | $\checkmark$ |

| tQSL                  |              |              |              |              |              |         |         |                      | $\sqrt{1}$ | √1,2         |              |        |       |                      |              |

NOTE: 1 = Single Ended signal; 2 = Differential signal; 3 = 2 x Single Ended signal

| TEST                   | Cycle        |              |              | Base         | d on '       | Test De      | efiniti      | on                   | R          | lequire      | d to P           | erform     | on Sc      | ope                  | Opt.         |

|------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|----------------------|------------|--------------|------------------|------------|------------|----------------------|--------------|

|                        | Read         | Write        | DQ           | DQS          | CK           | ADD          | Ctrl         | Data<br>Mask<br>Ctrl | DQ         | DQS          | CK               | ADD        | Ctrl       | Data<br>Mask<br>Ctrl | CS#          |

| tDQSS Low<br>Power     |              | $\checkmark$ |              | $\checkmark$ |              |              |              |                      | $\sqrt{1}$ | √1,2         | √1,2             |            |            |                      | $\checkmark$ |

| tDVAC<br>(Strobe)      |              | $\checkmark$ |              | $\checkmark$ |              |              |              |                      | $\sqrt{1}$ | $\sqrt{2}$   |                  |            |            |                      | $\checkmark$ |

| tDS(base)              |              | $\checkmark$ | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{2}$   |                  |            |            | $\sqrt{1}$           | $\checkmark$ |

| tDS(derate)            |              | $\checkmark$ | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{2}$   |                  |            |            | $\sqrt{1}$           | $\checkmark$ |

| tDH(base)              |              | $\checkmark$ | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{2}$   |                  |            |            | $\sqrt{1}$           | $\checkmark$ |

| tDH(derate)            |              | $\checkmark$ | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{2}$   |                  |            |            | $\sqrt{1}$           | $\checkmark$ |

| tDS1(base)             |              | $\checkmark$ | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{1}$   |                  |            |            | $\sqrt{1}$           | $\checkmark$ |

| tDS1(derate)           |              | $\checkmark$ | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{1}$   |                  |            |            | $\sqrt{1}$           | $\checkmark$ |

| tDH1(base)             |              | $\checkmark$ | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{1}$   |                  |            |            | $\sqrt{1}$           | $\checkmark$ |

| tDH1(derate)           |              | $\checkmark$ | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{1}$   |                  |            |            | $\sqrt{1}$           | $\checkmark$ |

| tVAC(Data)             |              | $\checkmark$ | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |                  |            |            |                      | $\checkmark$ |

| tDIPW                  |              | $\checkmark$ | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |                  |            |            |                      | $\checkmark$ |

| tQHP                   | $\checkmark$ |              | $\checkmark$ |              |              |              |              |                      | $\sqrt{1}$ | $\sqrt{1,2}$ |                  |            |            |                      | $\checkmark$ |

| tlS(base)              |              | $\checkmark$ |              |              |              |              |              |                      |            |              | √ <sup>1,2</sup> | $\sqrt{1}$ | $\sqrt{1}$ |                      | $\checkmark$ |

| tlS(derate)            |              | $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |                      |            |              | $\sqrt{1,2}$     | $\sqrt{1}$ | $\sqrt{1}$ |                      | $\checkmark$ |

| tIH(base)              |              | $\checkmark$ |              |              |              | $\checkmark$ | $\checkmark$ |                      |            |              | $\sqrt{1,2}$     | $\sqrt{1}$ | $\sqrt{1}$ |                      | $\checkmark$ |

| tIH(derate)            |              | $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |                      |            |              | $\sqrt{1,2}$     | $\sqrt{1}$ | $\sqrt{1}$ |                      | $\checkmark$ |

| tVAC<br>(CS,CA)        |              | $\checkmark$ |              |              |              |              | $\checkmark$ |                      |            |              |                  | $\sqrt{1}$ | $\sqrt{1}$ |                      |              |

| Eye Diagram<br>– Read  | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              |              |              |                      | $\sqrt{1}$ | √1,2         |                  |            |            |                      |              |

| Eye Diagram<br>– Write |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |                      | $\sqrt{1}$ | √1,2         |                  |            |            |                      |              |

NOTE: 1 = Single Ended signal; 2 = Differential signal; 3 = 2 x Single Ended signal

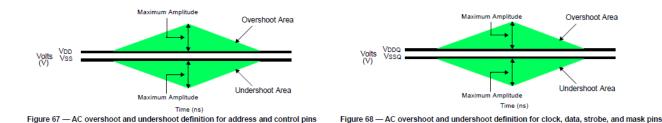

# DDR2(+LP) Compliance Test Application — At A Glance

The Agilent N5413B DDR2(+LP) Compliance Test Application is a DDR2 (Double Data Rate 2) and LPDDR2 (Low Power Double Data Rate 2) test solution that covers electrical, clock and timing parameters of the JEDEC (Joint Electronic Device Engineering Council) specifications. The software helps you in testing all the un-buffered DDR2/LPDDR2 device under test (DUT) compliance, with the Agilent Infinium oscilloscope.

There are 2 main categories of test modes:

- Compliance Tests These tests are based on the DDR2/LPDDR2 JEDEC compliance specifications and are compared to corresponding compliance test limits.

- Custom Mode Tests These tests are not based on any compliance specification. The primary use of these tests is to perform non-JEDEC specific speed signal testing.

The DDR2(+LP) Compliance Test Application:

- Lets you select individual or multiple tests to run.

- Lets you identify the device being tested and its configuration.

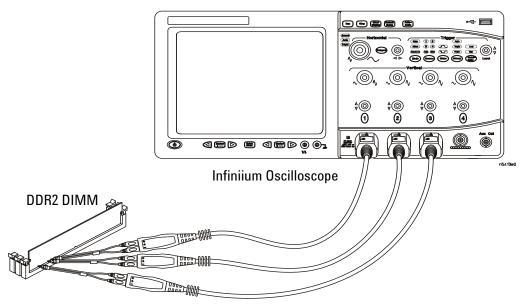

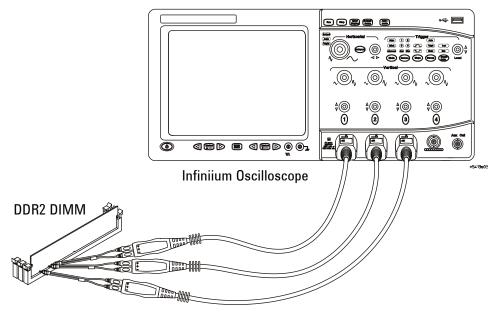

- Shows you how to make oscilloscope connections to the device under test.

- Automatically checks for proper oscilloscope configuration.

- Automatically sets up the oscilloscope for each test.

- Allows you to determine the number of trials for each test, with the new multi trial run capability.

- Allows you to customize the test limits in the application which determines the pass or/and fail of each test.

- Provides detailed information of each test that has been run. The result of maximum sixty four worst trials can be displayed at any one time.

- Creates a printable HTML report of the tests that have been run.

The minimum number of probes required for the tests are:

- Clock tests 1 probe.

- Electrical tests 3 probes.

- Clock Timing tests 3 probes.

- Custom Mode tests 3 probes.

**NOTE** The tests performed by the DDR2(+LP) Compliance Test Application are intended to provide a quick check of the physical layer performance of the DUT. These testing are not replacement for an exhaustive test validation plan.

DDR2(+LP) SDRAM electrical, clock and timing test standards and specifications are described in the *JESD79-2E*, *JESD208*, and *JESD209-2B* documents. For more information, refer to JEDEC web site at www.jedec.org.

#### **Required Equipment and Software**

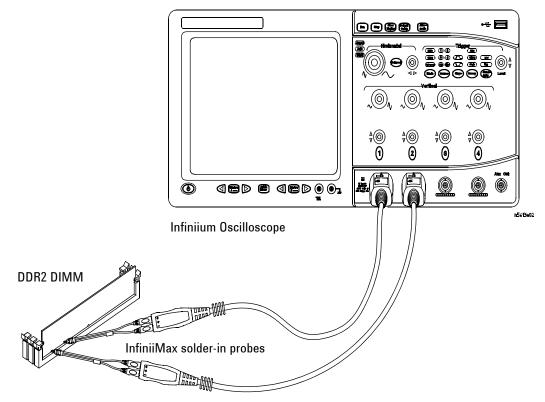

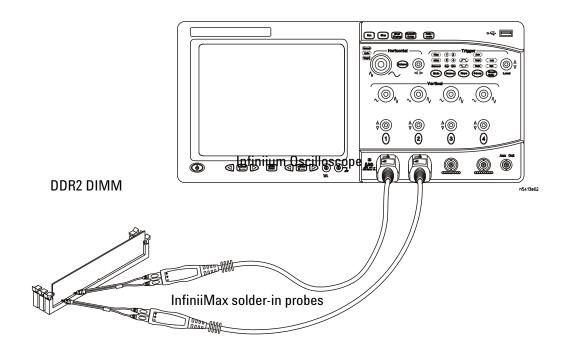

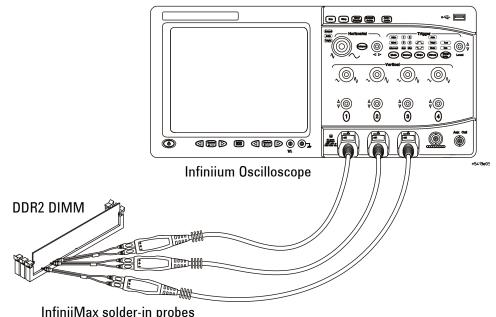

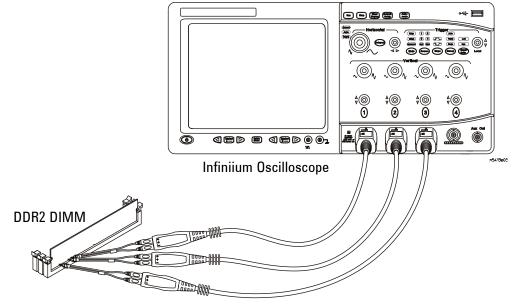

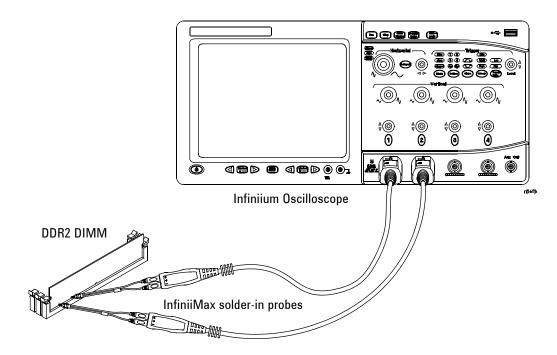

In order to run the DDR2(+LP) automated tests, you need the following equipment and software:

- The minimum version of Infiniium oscilloscope software (see the N5413B test application release notes).

- N5413B DDR2(+LP) Compliance Test Application, version 1.00 and higher.

- RAM reliability test software.

- 1169A, 1168A, 1134A, 1132A or 1131A InfiniiMax probe amplifiers.

- N5381A or E2677A differential solder-in probe head, N5382A or E2675A differential browser probe head, N5425A ZIF probe head with N5426A or N5451A ZIF tip accessories, E2678A differential socketed probe head.

- Any computer motherboard system that supports DDR2 memory.

- Keyboard, qty = 1, (provided with the Agilent Infiniium oscilloscope).

- Mouse, qty = 1, (provided with the Agilent Infiniium oscilloscope).

Below are the required licenses:

- N5413B DDR2(+LP) Compliance Test Application license.

- N5414A InfiniiScan software license.

- E2688A Serial Data Analysis and Clock Recovery software license.

- N5404A Deep memory option (optional).

# In This Book

This manual describes the tests that are performed by the DDR2(+LP) Compliance Test Application in more detail; it contains information from (and refers to) the *JESD79-2E*, *JESD208*, and *JESD209-2B* and it describes how the tests are performed.

- Chapter 1, "Installing the DDR2(+LP) Compliance Test Application" shows how to install and license the automated test application software (if it was purchased separately).

- Chapter 2, "Preparing to Take Measurements" shows how to start the DDR2(+LP) Compliance Test Application and gives a brief overview of how it is used.

- Chapter 3, "Measurement Clock Tests" describes the measurement clock tests including clock period jitter, clock to clock period jitter, cumulative error, average HIGH and LOW pulse width, half period jitter and average clock period tests.

- Chapter 4, "Single-Ended Signals Input/Output Parameters Tests" shows how to run the single-ended signals AC input/output parameters tests. This chapter includes input signal minimum slew rate (rising) tests, input signal minimum slew rate (falling) tests, input/output logic HIGH tests, input/output logic LOW tests, and output rising/falling slew rate tests (40 ohm and 60 ohm).

- Chapter 5, "Single-Ended Signals VIH/VIL (Address, Control) Tests" describes the AC/DC input logic high/low tests (address, control).

- Chapter 6, "Single-Ended Signals VIH/VIL (Data, Mask) Tests" describes the AC/DC input logic high/low tests (data, mask).

- Chapter 7, "Single-Ended Signals AC Parameters Tests for Strobe Signals" describes the V<sub>SEH(AC)</sub> and V<sub>SEL(AC)</sub> tests for strobe signals.

- Chapter 8, "Single-Ended Signals AC Parameters Tests for Clocks" describes the  $V_{SEH(AC)}$  and  $V_{SEL(AC)}$  tests for clocks.

- Chapter 9, "Single-Ended Signals Overshoot/Undershoot Tests" describes the AC overshoot and undershoot tests probing and method of implementation.

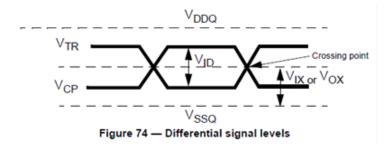

- Chapter 10, "Differential Signals AC Input Parameters Tests" describes the  $V_{ID}$  AC differential input voltage tests and  $V_{IX}$  AC differential cross point voltage tests. The  $V_{IHdiff}$  and  $V_{ILdiff}$  tests for both AC and DC are also described.

- Chapter 11, "Differential Signal AC Output Parameters Tests" contains information on the  $V_{OX}$  AC differential cross point voltage tests. It also describes the SRQdiffR (40 and 60 ohm), SQRdiffF (40 and 60 ohm),  $V_{OHdiff(AC)}$ , and  $V_{OLdiff(AC)}$  tests.

- Chapter 12, "Differential Signals Clock Cross Point Voltage Tests" describes the  $\rm V_{IXCA}$  Clock Cross Point Voltage test.

- Chapter 13, "Differential Signals Strobe Cross Point Voltage Tests" describes the  $V_{IXDQ}$  Strobe Cross Point Voltage test.

- Chapter 14, "Clock Timing (CT) Tests" describes the clock timing operating conditions of DDR2/LPDDR2 SDRAM as defined in the specification.

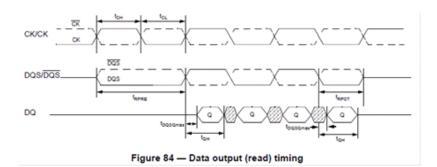

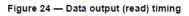

- Chapter 15, "Data Strobe Timing (DST) Tests" describes various data strobe timing tests including tHZ(DQ), tLZ(DQS), tLZ(DQ), tDQSQ, tQH, tDQSS, tDQSH, tDQSL, tDSS, tDSH, tWPST, tWPRE, tRPRE, tRPST, tHZ(DQ) Low Power, tHZ(DQS) Low Power, tLZ(DQS) Low Power, tLZ(DQ) Low Power, tQSH, tQSL, tDQSS, and tDVAC (Strobe) tests.

- Chapter 16, "Data Timing Tests" describes the measurement clock tests including clock period jitter, clock to clock period jitter, cumulative error, average HIGH and LOW pulse width, half period jitter and average clock period tests.

- Chapter 17, "Command and Address Timing (CAT) Tests" describes the measurement clock tests including clock period jitter, clock to clock period jitter, cumulative error, average HIGH and LOW pulse width, half period jitter and average clock period tests.

- Chapter 18, "Custom Mode Read-Write Eye-Diagram Tests" describes the user defined real-time eye-diagram test for read cycle and write cycle.

- Chapter 19, "Calibrating the Infinitum Oscilloscope and Probe" describes how to calibrate the oscilloscope in preparation for running the DDR2(+LP) automated tests.

- Chapter 20, "InfiniiMax Probing" describes the probe amplifier and probe head recommendations for DDR2(+LP) testing.

#### See Also

The DDR2(+LP) Compliance Test Application's online help, which describes:

- Starting the DDR2(+LP) compliance test application.

- To view/minimize the task flow pane

- To view/hide the toolbar

- Creating or Opening a Test Project

- Setting up DDR2(+LP) test environment.

- Selecting tests.

- Configuring tests.

- User-Defined compliance limits.

- Connecting the oscilloscope to the DUT.

- Running tests.

- Viewing test results.

- To delete trials from the results

- To show reference images and flash mask hits

- To change the display settings

- To change the remote settings

- To change the margin thresholds and trial report display

- To change the user prompt option

- To change the auto-recovery option

- Viewing/printing the HTML test report.

- Understanding the HTML report.

- Saving test projects.

# **Contact Agilent**

For more information on DDR2(+LP) Compliance Test Application or other Agilent Technologies' products, applications and services, contact your local Agilent office. The complete list is available at:

#### www.agilent.com/find/contactus

#### **Phone or Fax**

| United States:         |

|------------------------|

| (tel) 800 829 4444     |

| (fax) 800 829 4433     |

| Canada:                |

| (tel) 877 894 4414     |

| (fax) 800 746 4866     |

| China:                 |

| (tel) 800 810 0189     |

| (fax) 800 820 2816     |

| Europe:                |

| (tel) 31 20 547 2111   |

| Japan:                 |

| (tel) (81) 426 56 7832 |

| (fax) (81) 426 56 7840 |

|                        |

Korea: (tel) (080) 769 0800 (fax) (080) 769 0900 Latin America: (tel) (305) 269 7500 Taiwan: (tel) 0800 047 866 (fax) 0800 286 331 Other Asia Pacific Countries: (tel) (65) 6375 8100 (fax) (65) 6755 0042 E-mail: tm\_ap@agilent.com

# Contents

DDR2/LPDDR2 — Quick Reference 3 DDR2(+LP) Compliance Test Application — At A Glance 8 Required Equipment and Software 9 In This Book 10 See Also 11 Contact Agilent 13 Phone or Fax 13

#### 1 Installing the DDR2(+LP) Compliance Test Application

Installing the Software 35 Installing the License Key 35

#### **2** Preparing to Take Measurements

Calibrating the Oscilloscope 38 Starting the DDR2(+LP) Compliance Test Application 39 Online Help Topics 40

#### **3** Measurement Clock Tests

**Probing for Measurement Clock Tests** 44 **Test Procedure** 44 Clock Period Jitter - tJIT(per) - Test Method of Implementation 47 Signals of Interest 47 Test Definition Notes from the Specification 48 **Test References** 48 **Pass Condition** 48 Measurement Algorithm 48 Cycle to Cycle Period Jitter - tJIT(cc) - Test Method of Implementation 50 Signals of Interest 50 Test Definition Notes from the Specification 51 **Test References** 51 **Pass Condition** 51

Measurement Algorithm 51

```

53

Cumulative Error - tERR(n per) - Test Method of Implementation

Signals of Interest

53

Test Definition Notes from the Specification

54

55

Test References

Pass Condition

55

Measurement Algorithm

55

Cumulative Error (across 13-50 cycles) - tERR(13-50 per) (Low Power) - Test Method of

Implementation

57

Signals of Interest

57

Test Definition Notes from the Specification

57

Test References

57

Pass Condition

57

Measurement Algorithm

58

Average HIGH Pulse Width - tCH(avg) - Test Method of Implementation

59

Signals of Interest

59

Test Definition Notes from the Specification

60

60

Test References

Pass Condition

60

Measurement Algorithm

61

62

Absolute HIGH Pulse Width - tCH(abs) - Test Method of Implementation

Signals of Interest

62

Test Definition Notes from the Specification

62

Test References

62

Pass Condition

62

Measurement Algorithm

63

Average Low Pulse Width - tCL(avg) - Test Method of Implementation

64

Signals of Interest

64

Test Definition Notes from the Specification

65

Test References

65

Pass Condition

65

Measurement Algorithm

66

Absolute Low Pulse Width - tCL(abs) - Test Method of Implementation

67

Signals of Interest

67

Test Definition Notes from the Specification

67

Test References

67

Pass Condition

67

Measurement Algorithm

68

```

Half Period Jitter - tJIT(duty) - Test Method of Implementation 69 Signals of Interest 69 Test Definition Notes from the Specification 70 **Test References** 70 **Pass Condition** 70 **Measurement Algorithm** 70 Average Clock Period - tCK(avg) - Test Method of Implementation 72 Signals of Interest 72 Test Definition Notes from the Specification 73 Test References 73 Pass Condition 73 **Measurement Algorithm** 74 Absolute Clock Period - tCK(abs) - Test Method of Implementation 75 Signals of Interest 75 Test Definition Notes from the Specification 75 **Test References** 75

Pass Condition 75 Measurement Algorithm

#### 4 Single-Ended Signals Input/Output Parameters Tests

Probing for Single-Ended Signals Input/Output Parameters Tests 78 Test Procedure 79 VIH(AC) Test Method of Implementation 81 Signals of Interest 81 Test Definition Notes from the Specification 82 **Test References** 82 **PASS Condition** 82 Measurement Algorithm 82 VIH(DC) Test Method of Implementation 84 Signals of Interest 84 Test Definition Notes from the Specification 85 **Test References** 85 PASS Condition 85 Measurement Algorithm 85

76

```

VIL(AC) Test Method of Implementation

87

Signals of Interest

87

Test Definition Notes from the Specification

88

Test References

88

PASS Condition

88

Measurement Algorithm

88

VIL(DC) Test Method of Implementation

90

Signals of Interest

90

Test Definition Notes from the Specification

91

Test References

91

PASS Condition

91

Measurement Algorithm

91

SlewR Test Method of Implementation

93

Signals of Interest

93

Test Definition Notes from the Specification

93

Test References

94

PASS Condition

94

Measurement Algorithm

94

SlewF Test Method of Implementation

96

Signals of Interest

96

Test Definition Notes from the Specification

96

Test References

97

PASS Condition

97

Measurement Algorithm

97

SRQseR(40ohm) Test Method of Implementation

99

Signals of Interest

99

Test Definition Notes from the Specification

99

99

Test References

PASS Condition

99

100

Measurement Algorithm

SRQseF(40ohm) Test Method of Implementation

101

Signals of Interest

101

Test Definition Notes from the Specification

101

Test References

101

PASS Condition

101

Measurement Algorithm

102

```

```

SRQseR(60ohm) Test Method of Implementation

103

Signals of Interest

103

Test Definition Notes from the Specification

103

Test References

103

PASS Condition

103

Measurement Algorithm

104

SRQseF(60ohm) Test Method of Implementation

105

105

Signals of Interest

105

Test Definition Notes from the Specification

Test References

105

PASS Condition

105

Measurement Algorithm

106

VOH(AC) Test Method of Implementation

107

Signals of Interest

107

107

Test Definition Notes from the Specification

Test References

107

PASS Condition

108

Measurement Algorithm

108

VOH(DC) Test Method of Implementation

109

Signals of Interest

109

Test Definition Notes from the Specification

109

Test References

109

PASS Condition

110

Measurement Algorithm

110

VOL(AC) Test Method of Implementation

111

Signals of Interest

111

Test Definition Notes from the Specification

111

Test References

111

PASS Condition

112

Measurement Algorithm

112

VOL(DC) Test Method of Implementation

113

Signals of Interest

113

Test Definition Notes from the Specification

113

Test References

113

PASS Condition

114

Measurement Algorithm

114

```

#### 5 Single-Ended Signals VIH/VIL (Address, Control) Tests

Probing for Single-Ended Signals VIH/VIL (Address, Control) Tests 116 Test Procedure 116 VIHCA(AC) Test Method of Implementation 118 Signals of Interest 118 Test Definition Notes from the Specification 118 **Test References** 118 **PASS Condition** 119 **Measurement Algorithm** 119 VIHCA(DC) Test Method of Implementation 120 Signals of Interest 120 Test Definition Notes from the Specification 120 **Test References** 120 **PASS Condition** 121 Measurement Algorithm 121 VILCA(AC) Test Method of Implementation 122 Signals of Interest 122 Test Definition Notes from the Specification 122 **Test References** 122 PASS Condition 123 **Measurement Algorithm** 123 VILCA(DC) Test Method of Implementation 124 Signals of Interest 124 Test Definition Notes from the Specification 124 **Test References** 124 **PASS Condition** 125 Measurement Algorithm 125

#### 6 Single-Ended Signals VIH/VIL (Data, Mask) Tests

Probing for Single-Ended Signals VIH/VIL (Data, Mask) Tests 128 Test Procedure 129 VIHDQ(AC) Test Method of Implementation 131 Signals of Interest 131 Test Definition Notes from the Specification 131 **Test References** 131 PASS Condition 132 **Measurement Algorithm** 132

VIHDQ(DC) Test Method of Implementation 133 Signals of Interest 133 Test Definition Notes from the Specification 134 134 Test References **PASS Condition** 134 **Measurement Algorithm** 134 VILDQ(AC) Test Method of Implementation 135 Signals of Interest 135 Test Definition Notes from the Specification 135 Test References 135 PASS Condition 136 Measurement Algorithm 136 VILDQ(DC) Test Method of Implementation 137 Signals of Interest 137 Test Definition Notes from the Specification 138 **Test References** 138 **PASS Condition** 138

Measurement Algorithm 138

#### 7 Single-Ended Signals AC Parameters Tests for Strobe Signals

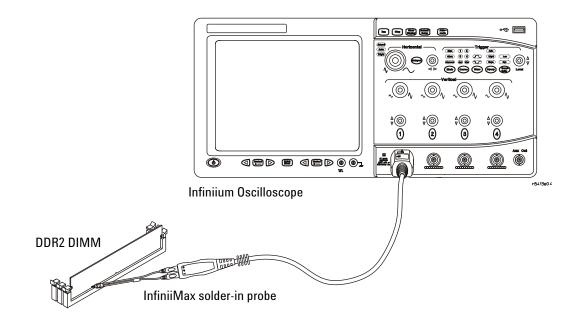

Probing for Single-Ended Signals AC Input Parameters Tests for Strobe Signals 140 Test Procedure 141 VSEH(AC) (strobe) Test Method of Implementation 143 Signals of Interest 143 Test Definition Notes from the Specification 143 **Test References** 143 **PASS Condition** 143 **Measurement Algorithm** 144 VSEL(AC) (strobe) Test Method of Implementation 145 Signals of Interest 145 Test Definition Notes from the Specification 145 **Test References** 145 PASS Condition 145 **Measurement Algorithm** 146

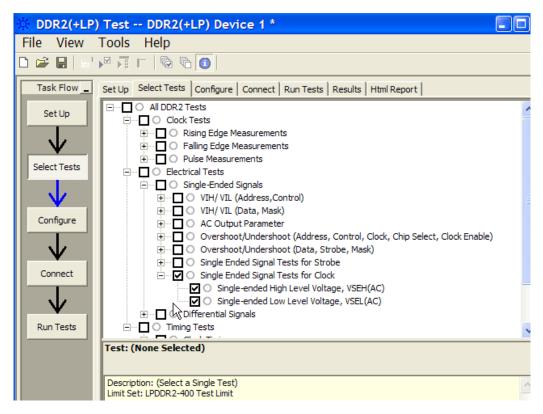

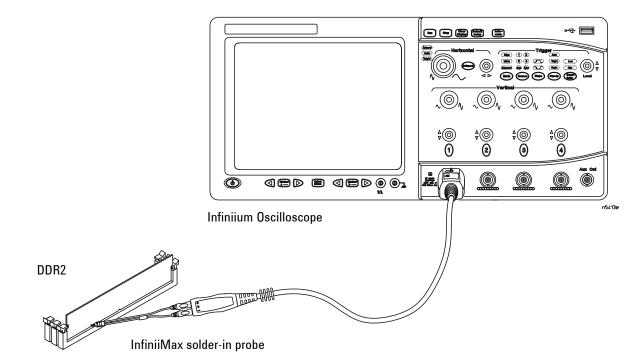

#### 8 Single-Ended Signals AC Parameters Tests for Clocks

Probing for Single-Ended Signals AC Input Parameters Tests for Clocks 148 Test Procedure 148

| VSEH(AC) (clock) Test Method of Implementation                             | 150       |

|----------------------------------------------------------------------------|-----------|

| Signals of Interest 150                                                    |           |

| Test Definition Notes from the Specification 15                            | 50        |

| Test References 150                                                        |           |

| PASS Condition 150                                                         |           |

| Measurement Algorithm 151                                                  |           |

|                                                                            |           |

| VSEL(AC) (clock) Test Method of Implementation                             | 152       |

| VSEL(AC) (clock) Test Method of Implementation<br>Signals of Interest 152  | 152       |

| Signals of Interest 152                                                    | 152<br>52 |

| Signals of Interest 152                                                    |           |

| Signals of Interest 152<br>Test Definition Notes from the Specification 15 |           |

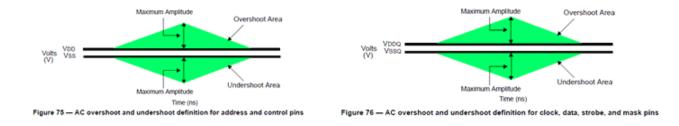

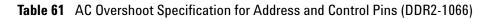

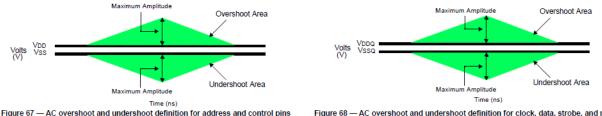

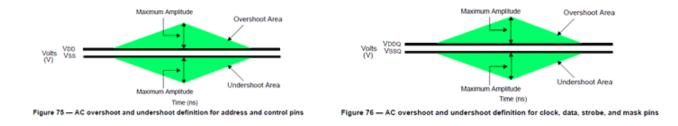

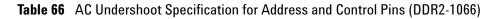

## 9 Single-Ended Signals Overshoot/Undershoot Tests

| Probing for Overshoot/Undershoot Tests 156<br>Test Procedure 156 |

|------------------------------------------------------------------|

| AC Overshoot Test Method of Implementation 158                   |

| Signals of Interest 158                                          |

| Test Definition Notes from the Specification 159                 |

| Test References 160                                              |

| PASS Condition 160                                               |

| Measurement Algorithm 161                                        |

| AC Undershoot Test Method of Implementation 162                  |

| Signals of Interest 162                                          |

| Test Definition Notes from the Specification 163                 |

| Test References 164                                              |

| PASS Condition 164                                               |

| Measurement Algorithm 165                                        |

### **10 Differential Signals AC Input Parameters Tests**

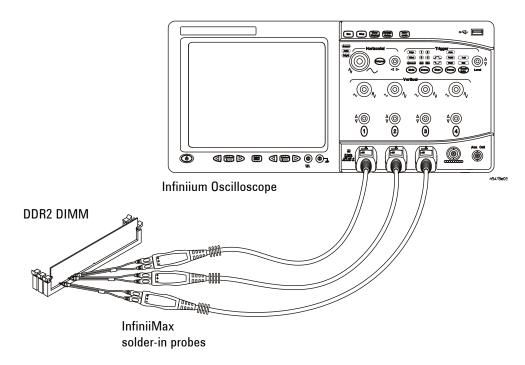

Probing for Differential Signals AC Input Parameters Tests 168

Test Procedure 168

VID(AC), AC Differential Input Voltage - Test Method of Implementation 170

Signals of Interest 170

Test Definition Notes from the Specification 170

Test References 171

PASS Condition 171

Measurement Algorithm 171

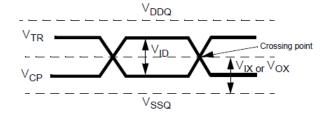

VIX(AC), AC Differential Input Cross Point Voltage - Test Method of Implementation 173 Signals of Interest 173 Test Definition Notes from the Specification 173 Test References 174 **PASS Condition** 174 Measurement Algorithm 174 VIHdiff(AC) Test Method of Implementation 176 Signals of Interest 176 Test Definition Notes from the Specification 177 Test References 177 **PASS Condition** 177 **Measurement Algorithm** 177 VIHdiff(DC) Test Method of Implementation 179 Signals of Interest 179 Test Definition Notes from the Specification 180 **Test References** 180 **PASS Condition** 180 **Measurement Algorithm** 180 VILdiff(AC) Test Method of Implementation 182 Signals of Interest 182 Test Definition Notes from the Specification 183 Test References 183 **PASS Condition** 183 **Measurement Algorithm** 183 VILdiff(DC) Test Method of Implementation 185 Signals of Interest 185 Test Definition Notes from the Specification 186 186 **Test References PASS Condition** 186 Measurement Algorithm 186

#### **11 Differential Signal AC Output Parameters Tests**

Probing for Differential Signals AC Output Parameters Tests 190 Test Procedure 190 VOX , AC Differential Output Cross Point Voltage - Test Method of Implementation 192 Signals of Interest 192 Test Definition Notes from the Specification 192 193 Test References **PASS** Condition 193 **Measurement Algorithm** 193 SRQdiffR(40ohm) Test Method of Implementation 194 Signals of Interest 194 Test Definition Notes from the Specification 194 Test References 194 PASS Condition 194 Measurement Algorithm 194 SRQdiffF(40ohm) Test Method of Implementation 196 Signals of Interest 196 Test Definition Notes from the Specification 196 **Test References** 196 **PASS** Condition 196 Measurement Algorithm 196 SRQdiffR(60ohm) Test Method of Implementation 198 Signals of Interest 198 Test Definition Notes from the Specification 198 Test References 198 **PASS Condition** 198 Measurement Algorithm 198 SRQdiffF(60ohm) Test Method of Implementation 200 Signals of Interest 200 Test Definition Notes from the Specification 200 200 **Test References PASS Condition** 200 200 Measurement Algorithm VOHdiff(AC) Test Method of Implementation 202 Signals of Interest 202 Test Definition Notes from the Specification 202 202 **Test References PASS Condition** 202 **Measurement Algorithm** 203

VOLdiff(AC) Test Method of Implementation 204 Signals of Interest 204 Test Definition Notes from the Specification 204 Test References 204 PASS Condition 204 Measurement Algorithm 205

#### 12 Differential Signals Clock Cross Point Voltage Tests

Probing for Differential Signals Clock Cross Point Voltage Tests 208 Test Procedure 208 VIXCA, Clock Cross Point Voltage - Test Method of Implementation 210 Signals of Interest 210 Test Definition Notes from the Specification 210 Test References 210 PASS Condition 210 Measurement Algorithm 210

#### 13 Differential Signals Strobe Cross Point Voltage Tests

Probing for Differential Signals Strobe Cross Point Voltage Tests 214 Test Procedure 214

VIXDQ, Strobe Cross Point Voltage - Test Method of Implementation 216 Signals of Interest 216 Test Definition Notes from the Specification 216 Test References 216 PASS Condition 216 Measurement Algorithm 216

#### 14 Clock Timing (CT) Tests

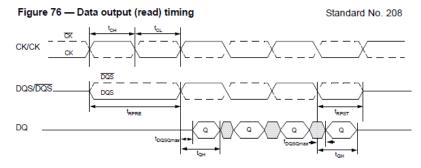

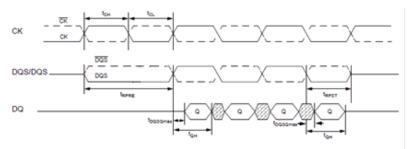

**Probing for Clock Timing Tests** 220 Test Procedure 220 tAC, DQ Output Access Time from CK/CK# - Test Method of Implementation 222 Signals of Interest 222 Test Definition Notes from the Specification 223 **Test References** 223 PASS Condition 223 **Measurement Algorithm** 223

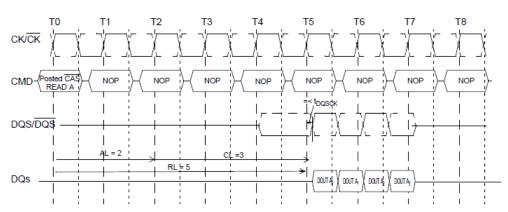

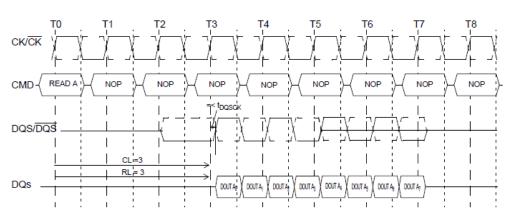

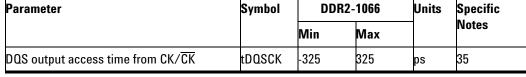

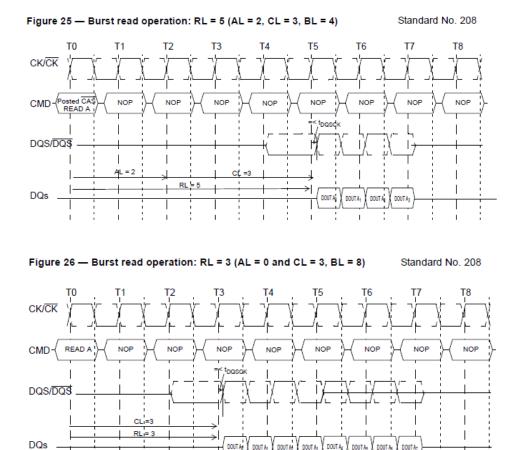

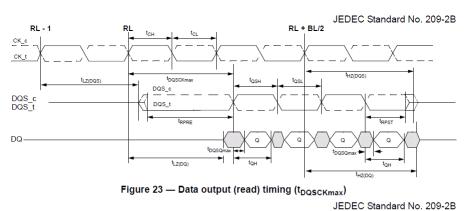

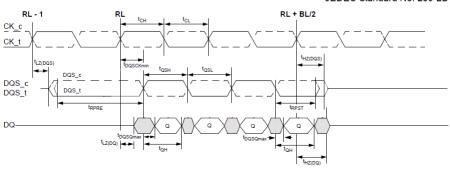

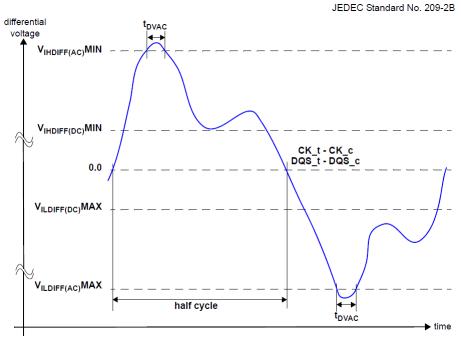

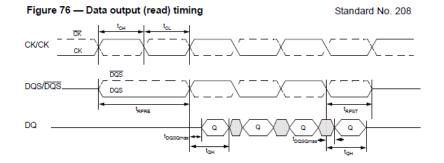

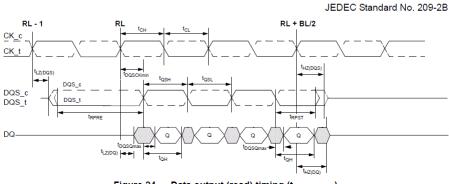

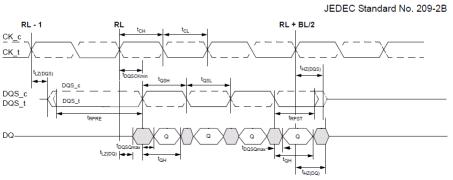

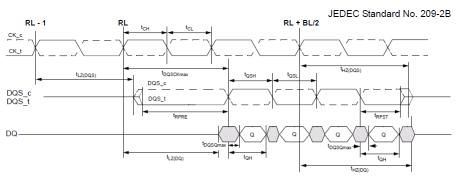

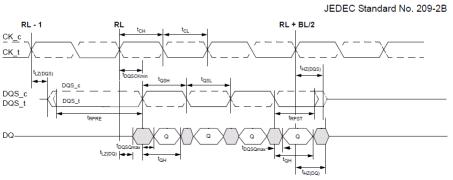

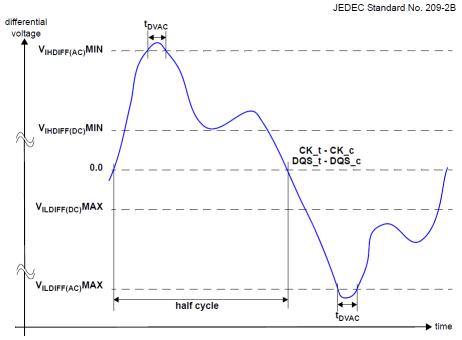

tDQSCK, DQS Output Access Time from CK/CK# - Test Method of Implementation 224 Signals of Interest 224 Test Definition Notes from the Specification 225 Test References 226 **PASS Condition** 226 **Measurement Algorithm** 227 tDQSCK (Low Power), DQS Output Access Time from CK\_t, CK\_c - Test Method of Implementation 228 Signals of Interest 228 Test Definition Notes from the Specification 229 **Test References** 229 PASS Condition 229 **Measurement Algorithm** 230 tDVAC (Clock), Time Above VIHdiff(AC)/below VILdiff(AC) - Test Method of Implementation 231 Signals of Interest 231 Test Definition Notes from the Specification 232 **Test References** 233 PASS Condition 233 **Measurement Algorithm** 233 234 tQHS, Data Hold Skew Factor - Test Method of Implementation Signals of Interest 234 Test Definition Notes from the Specification 234

Measurement Algorithm 235

234

235

**Test References**

PASS Condition

#### 15 Data Strobe Timing (DST) Tests

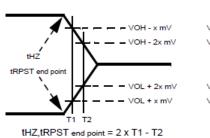

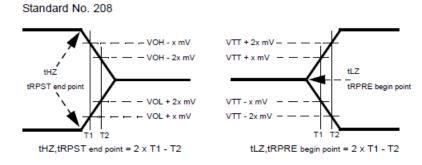

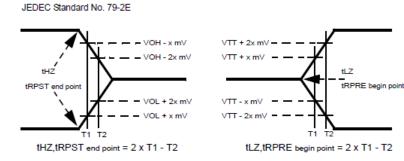

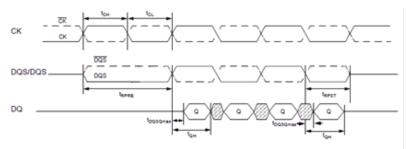

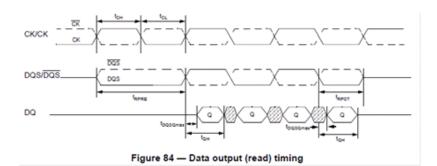

Probing for Data Strobe Timing Tests 239 Test Procedure 239 tHZ(DQ), DQ Out HIGH Impedance Time From CK/CK# - Test Method of Implementation 241 Signals of Interest 241 Test Definition Notes from the Specification 242 **Test References** 243 PASS Condition 243 Measurement Algorithm 243

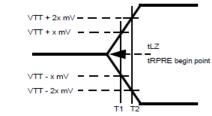

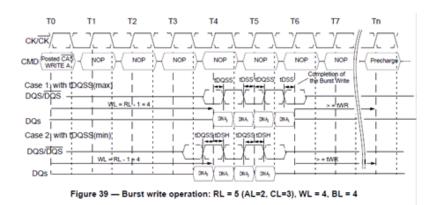

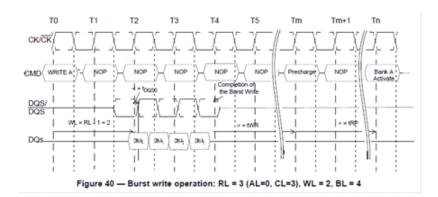

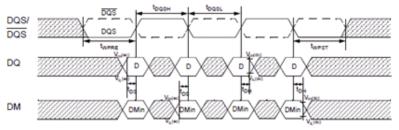

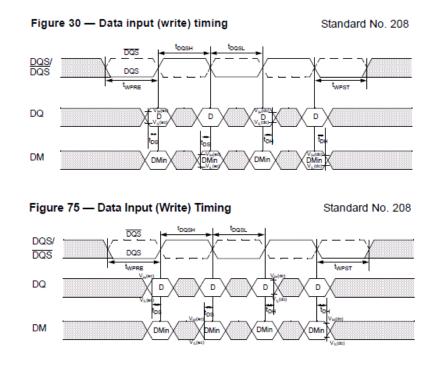

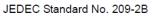

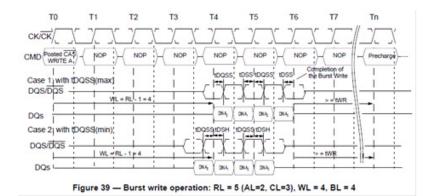

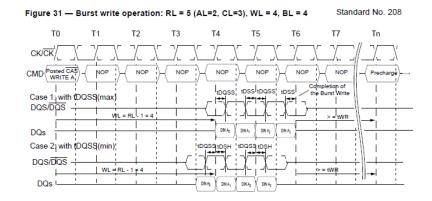

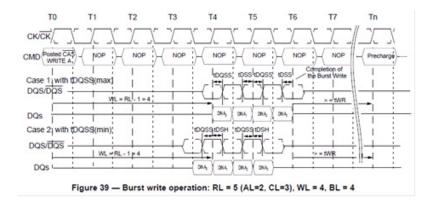

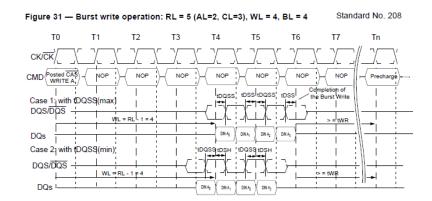

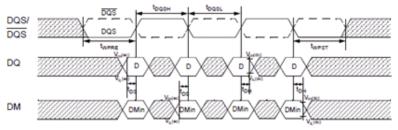

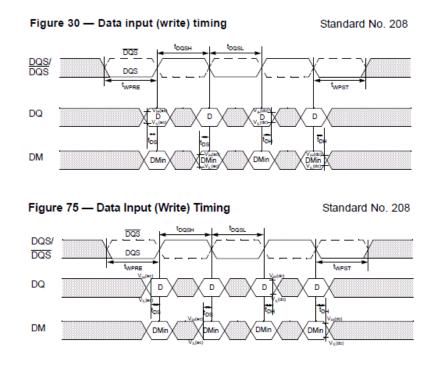

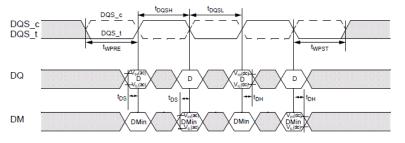

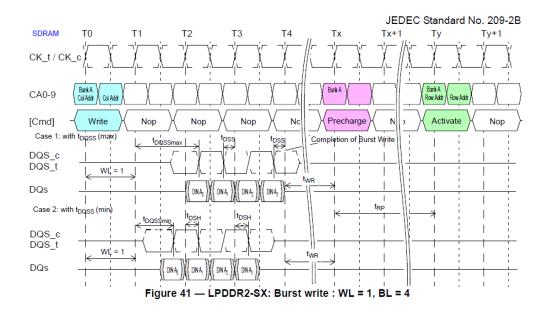

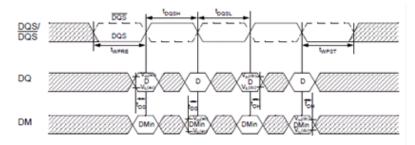

244 tLZ(DQS), DQS Low-Impedance Time from CK/CK# - Test Method of Implementation Signals of Interest 244 Test Definition Notes from the Specification 245 Test References 246 **PASS Condition** 246 **Measurement Algorithm** 246 tLZ(DQ), DQ Low-Impedance Time from CK/CK# - Test Method of Implementation 247 Signals of Interest 247 Test Definition Notes from the Specification 248 Test References 249 PASS Condition 249 Measurement Algorithm 249 tDQSQ, DQS-DQ Skew for DQS and Associated DQ Signals - Test Method of Implementation 250 250 Signals of Interest Test Definition Notes from the Specification 251 Test References 252 PASS Condition 252 **Measurement Algorithm** 253 tQH, DQ/DQS Output Hold Time From DQS - Test Method of Implementation 254 254 Signals of Interest Test Definition Notes from the Specification 255 **Test References** 256 **PASS Condition** 256 **Measurement Algorithm** 257 tDQSS, DQS Latching Transition to Associated Clock Edge - Test Method of Implementation 258 Signals of Interest 258 Test Definition Notes from the Specification 259 **Test References** 261 PASS Condition 261 **Measurement Algorithm** 261 tDQSH, DQS Input HIGH Pulse Width - Test Method of Implementation 263 Signals of Interest 263 Test Definition Notes from the Specification 264 Test References 266 **PASS Condition** 266 **Measurement Algorithm** 266

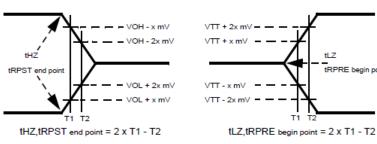

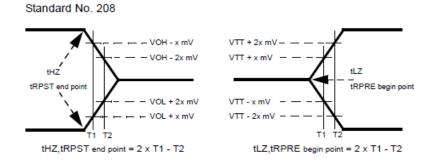

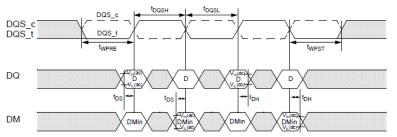

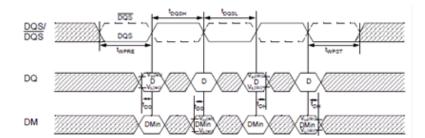

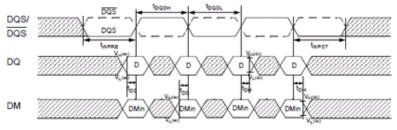

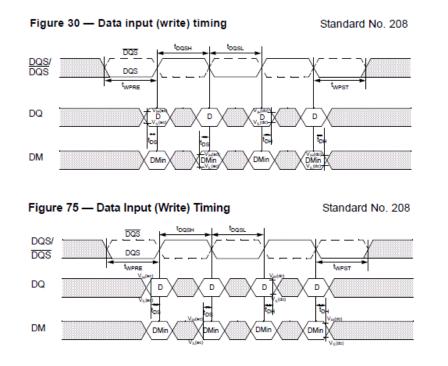

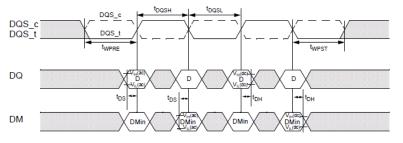

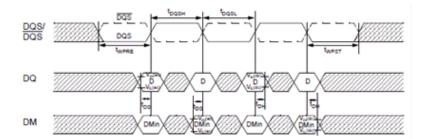

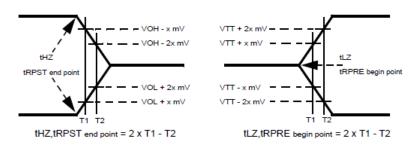

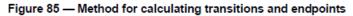

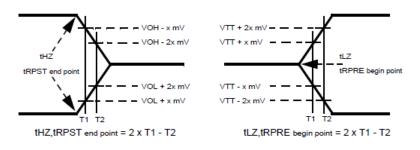

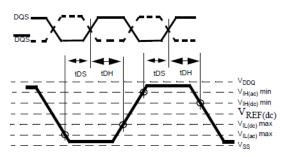

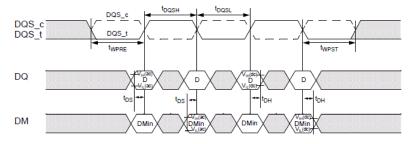

tDQSL, DQS Input Low Pulse Width - Test Method of Implementation 267 Signals of Interest 267 Test Definition Notes from the Specification 268 270 Test References **PASS Condition** 270 Measurement Algorithm 270 tDSS, DQS Falling Edge to CK Setup Time - Test Method of Implementation 271 Signals of Interest 271 Test Definition Notes from the Specification 272 Test References 273 PASS Condition 273 Measurement Algorithm 273 tDSH, DQS Falling Edge Hold Time from CK - Test Method of Implementation 275 Signals of Interest 275 Test Definition Notes from the Specification 276 **Test References** 277 **PASS Condition** 277 Measurement Algorithm 277 tWPST, Write Postamble - Test Method of Implementation 279 Signals of Interest 279 Test Definition Notes from the Specification 280 Test References 281 **PASS Condition** 282 **Measurement Algorithm** 282 tWPRE, Write Preamble - Test Method of Implementation 283 Signals of Interest 283 Test Definition Notes from the Specification 284 **Test References** 285 **PASS Condition** 286 286 Measurement Algorithm tRPRE, Read Preamble - Test Method of Implementation 287 Signals of Interest 287 Test Definition Notes from the Specification 288 290 **Test References PASS Condition** 290 **Measurement Algorithm** 291

tRPST, Read Postamble - Test Method of Implementation 292 Signals of Interest 292 Test Definition Notes from the Specification 293 295 Test References **PASS Condition** 295 **Measurement Algorithm** 296 tHZ(DQ) Test (Low Power), DQ Out HIGH Impedance Time From Clock - Test Method of Implementation 297 Signals of Interest 297 Test Definition Notes from the Specification 298 **Test References** 298 PASS Condition 298 **Measurement Algorithm** 299 tHZ(DQS) Test (Low Power), DQS Out HIGH Impedance Time From Clock - Test Method of Implementation 300 Signals of Interest 300 Test Definition Notes from the Specification 301 **Test References** 301 PASS Condition 301 **Measurement Algorithm** 302 tLZ(DQS) Test (Low Power), DQS Low-Impedance Time from Clock - Test Method of Implementation 303 303 Signals of Interest Test Definition Notes from the Specification 304 Test References 304 **PASS Condition** 304 **Measurement Algorithm** 305 tLZ(DQ) Test (Low Power), DQ Low-Impedance Time from Clock - Test Method of Implementation 306 306 Signals of Interest Test Definition Notes from the Specification 307 **Test References** 307 PASS Condition 307 308 **Measurement Algorithm** tQSH, DQS Output High Pulse Width - Test Method of Implementation 309 Signals of Interest 309 Test Definition Notes from the Specification 310 **Test References** 310 PASS Condition 310 Measurement Algorithm 311

tQSL, DQS Output Low Pulse Width - Test Method of Implementation 312 Signals of Interest 312 Test Definition Notes from the Specification 313 Test References 313 PASS Condition 313 Measurement Algorithm 314

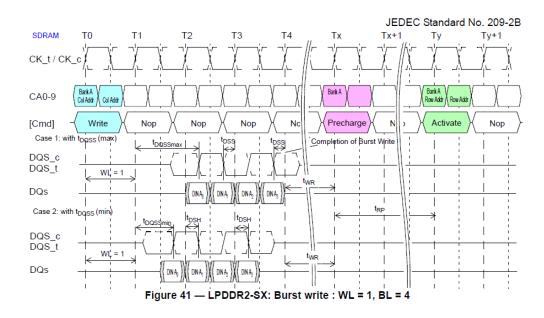

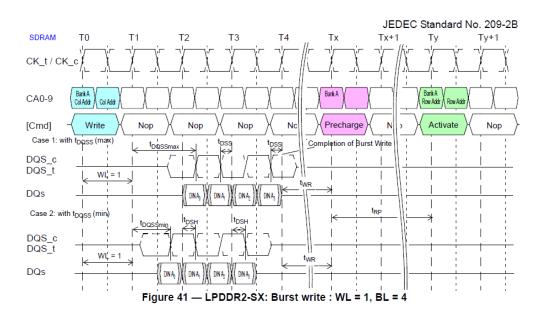

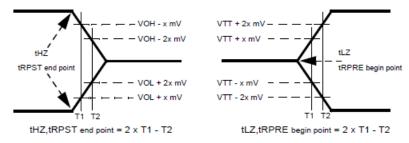

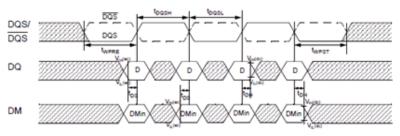

tDQSS Test (Low Power), DQS Latching Transition to Associated Clock Edge - Test Method of Implementation 315 Signals of Interest 315 Test Definition Notes from the Specification 316 Test References 316 PASS Condition 316 Measurement Algorithm 316

tDVAC (Strobe), Time Above VIHdiff(AC)/below VILdiff(AC) - Test Method of Implementation 318 Signals of Interest 318 Test Definition Notes from the Specification 319 Test References 320 PASS Condition 320 Measurement Algorithm 320

#### **16 Data Timing Tests**

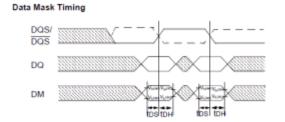

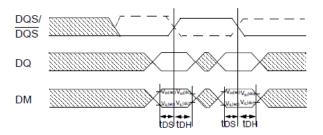

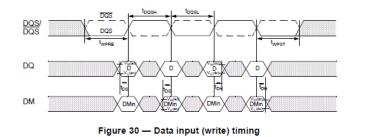

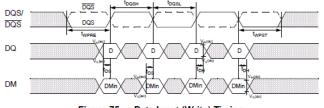

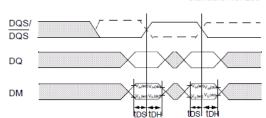

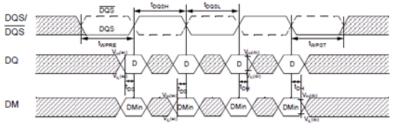

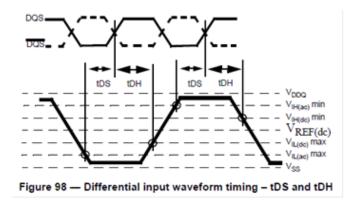

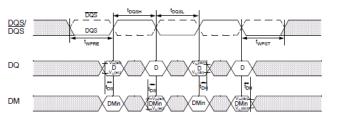

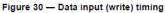

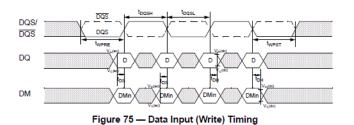

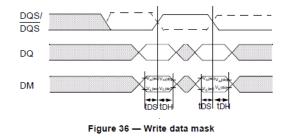

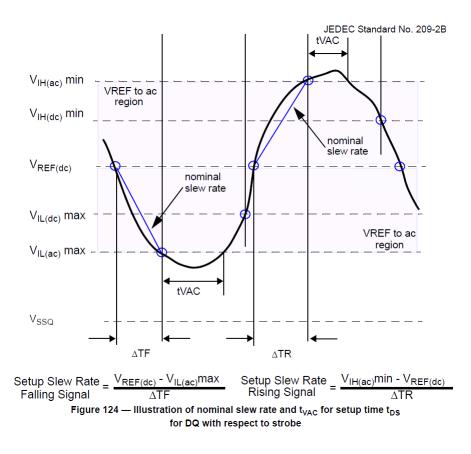

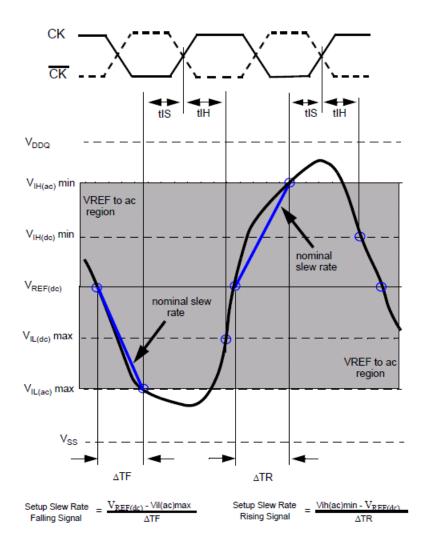

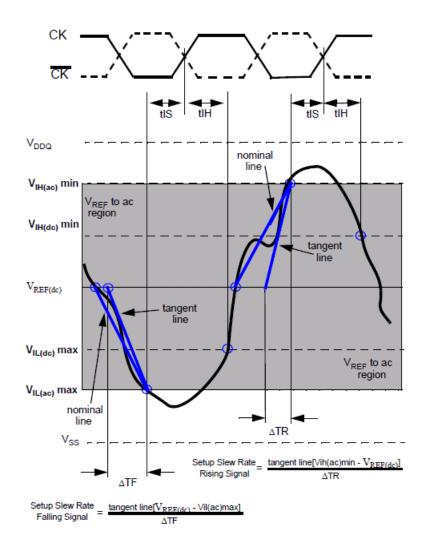

**Probing for Data Timing Tests** 322 Test Procedure 322 tDS(base), Differential DQ and DM Input Setup Time - Test Method of Implementation 325 325 Signals of Interest Test Definition Notes from the Specification 326 Test References 328 **PASS Condition** 328 328 Measurement Algorithm tDH(base), Differential DQ and DM Input Hold Time - Test Method of Implementation 330 Signals of Interest 330 Test Definition Notes from the Specification 331 **Test References** 333 PASS Condition 333 **Measurement Algorithm** 333

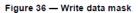

tDS(derate), Differential DQ and DM Input Setup Time with Derating Support - Test Method of Implementation 335 335 Signals of Interest Test Definition Notes from the Specification 335 Test References 346 PASS Condition 347 **Measurement Algorithm** 347 tDH(derate), Differential DQ and DM Input Hold Time with Derating Support - Test Method of Implementation 348 348 Signals of Interest Test Definition Notes from the Specification 348 Test References 359 **PASS Condition** 360 Measurement Algorithm 360 tDS1(base), Single-Ended DQ and DM Input Setup Time - Test Method of Implementation 361 Signals of Interest 361 Test Definition Notes from the Specification 361 **Test References** 361 **PASS Condition** 361 Measurement Algorithm 362 tDH1(base), Single-Ended DQ and DM Input Hold Time - Test Method of Implementation 363 Signals of Interest 363 Test Definition Notes from the Specification 363 363 **Test References** PASS Condition 363 **Measurement Algorithm** 364 tDS1(derate), Single-Ended DQ and DM Input Setup Time with Derating Support - Test Method of Implementation 365 Signals of Interest 365 Test Definition Notes from the Specification 365 **Test References** 368 **PASS Condition** 368 Measurement Algorithm 369

tDH1(derate), Single-Ended DQ and DM Input Hold Time with Derating Support - Test Method of Implementation 370 370 Signals of Interest Test Definition Notes from the Specification 370 Test References 373 PASS Condition 373 Measurement Algorithm 374 tVAC (Data), Time Above VIH(AC)/below VIL(AC) - Test Method of Implementation 375 Signals of Interest 375 Test Definition Notes from the Specification 376 **Test References** 377 **PASS Condition** 377 **Measurement Algorithm** 377 tDIPW, DQ and DM Input Pulse Width - Test Method of Implementation 378 Signals of Interest 378 Test Definition Notes from the Specification 378 Test References 378 PASS Condition 378 **Measurement Algorithm** 379 tQHP, Data Half Period - Test Method of Implementation 380 380 Signals of Interest Test Definition Notes from the Specification 380 **Test References** 380 **PASS Condition** 380 Measurement Algorithm 381 17 Command and Address Timing (CAT) Tests **Probing for Command Address Timing Tests** 384

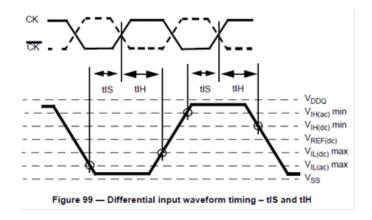

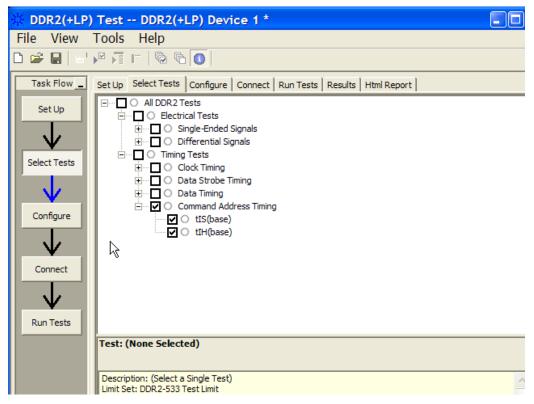

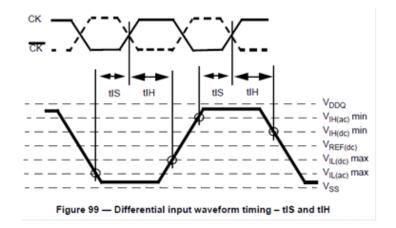

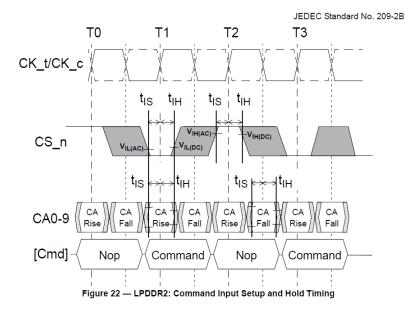

# Test Procedure 384 tlS(base) - Address and Control Input Setup Time - Test Method of Implementation 386 Signals of Interest 386 Test Definition Notes from the Specification 387 Test References 388 PASS Condition 388 Measurement Algorithm 389

tIH(base) - Address and Control Input Hold Time - Test Method of Implementation 390 Signals of Interest 390 Test Definition Notes from the Specification 391 Test References 392 PASS Condition 392 Measurement Algorithm 393

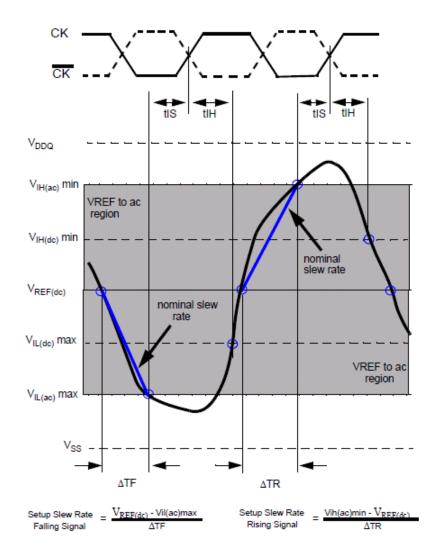

tlS(derate) - Address and Control Input Setup Time with Derating Support - Test Method of Implementation 394 Signals of Interest 394 Test Definition Notes from the Specification 394 Test References 405 PASS Condition 406 Measurement Algorithm 406

tlH(derate) - Address and Control Input Hold Time with Derating Support - Test Method of Implementation 407 Signals of Interest 407 Test Definition Notes from the Specification 407 Test References 418 PASS Condition 419 Measurement Algorithm 419

tVAC (CS, CA), Time Above VIH(AC)/below VIL(AC) - Test Method of Implementation 420

Signals of Interest 420

Test Definition Notes from the Specification 421

Test References 422

PASS Condition 422

Measurement Algorithm 422

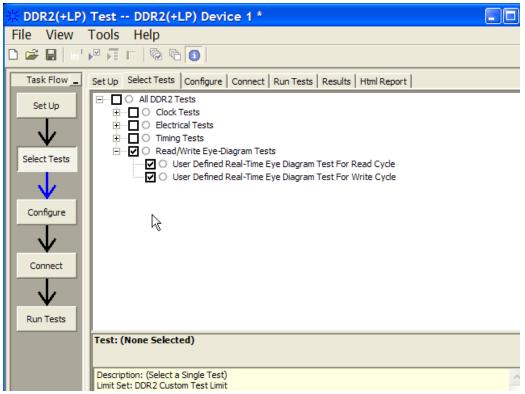

### 18 Custom Mode Read-Write Eye-Diagram Tests

Probing for Custom Mode Read-Write Eye Diagram Tests 426 Test Procedure 426

User Defined Real-Time Eye Diagram Test for Read Cycle Method of Implementation 430 Signals of Interest 430 Measurement Algorithm 430

User Defined Real-Time Eye Diagram Test for Write Cycle Method of Implementation 432 Signals of Interest 432

Measurement Algorithm 432

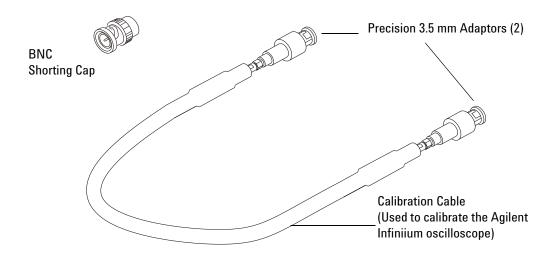

### **19** Calibrating the Infiniium Oscilloscope and Probe

Required Equipment for Oscilloscope Calibration 435 Internal Calibration 436 Required Equipment for Probe Calibration 439 Probe Calibration 440 Connecting the Probe for Calibration 440 Verifying the Connection 442 Running the Probe Calibration and Deskew 444 Verifying the Probe Calibration 446

### 20 InfiniiMax Probing

Index

N5413B DDR2(+LP) Compliance Test Application Compliance Testing Methods of Implementation

# Installing the DDR2(+LP) Compliance Test Application

Installing the Software 35 Installing the License Key 35

If you purchased the N5413B DDR2(+LP) Compliance Test Application separately, you need to install the software and license key.

# **Installing the Software**

- 1 Make sure you have the minimum version of Infiniium oscilloscope software (see the N5413B test application release notes) by choosing Help>About Infiniium... from the main menu.

- **2** To obtain the DDR2(+LP) Compliance Test Application, go to Agilent website: <u>http://www.agilent.com/find/N5413B</u>.

- **3** The link for DDR2(+LP) Compliance Test Application will appear. Double-click on it and follow the instructions to download and install the application software.

# **Installing the License Key**

**1** Request a license code from Agilent by following the instructions on the Entitlement Certificate.

You will need the oscilloscope's "Option ID Number", which you can find in the **Help>About Infiniium...** dialog box.

- 2 After you receive your license code from Agilent, choose Utilities>Install Option License....

- **3** In the Install Option License dialog, enter your license code and click **Install License**.

- **4** Click **OK** in the dialog that tells you to restart the Infiniium oscilloscope application software to complete the license installation.

- 5 Click Close to close the Install Option License dialog.

- 6 Choose File>Exit.

### **1** Installing the DDR2(+LP) Compliance Test Application

**7** Restart the Infiniium oscilloscope application software to complete the license installation.

2

N5413B DDR2(+LP) Compliance Test Application Compliance Testing Methods of Implementation

## **Preparing to Take Measurements**

Calibrating the Oscilloscope 38 Starting the DDR2(+LP) Compliance Test Application 39

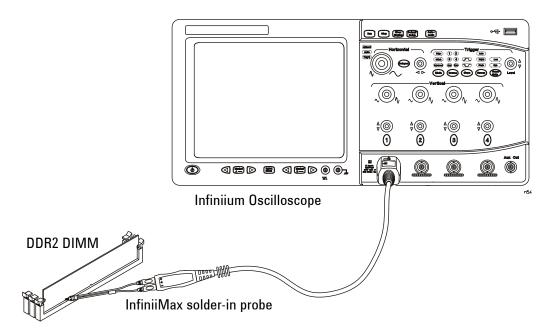

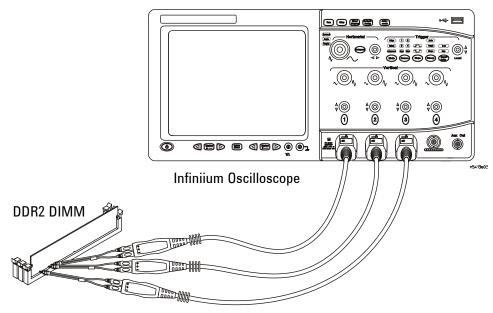

Before running the DDR2(+LP) automated tests, you should calibrate the oscilloscope and probe. No test fixture is required for this DDR2(+LP) application. After the oscilloscope and probe have been calibrated, you are ready to start the DDR2(+LP) Compliance Test Application and perform the measurements.

#### **2** Preparing to Take Measurements

## **Calibrating the Oscilloscope**

If you haven't already calibrated the oscilloscope and probe, see Chapter 19, "Calibrating the Infiniium Oscilloscope and Probe".

**NOTE** If the ambient temperature changes more than 5 degrees Celsius from the calibration temperature, internal calibration should be performed again. The delta between the calibration temperature and the present operating temperature is shown in the Utilities>Calibration menu.

# **NOTE** If you switch cables between channels or other oscilloscopes, it is necessary to perform cable and probe calibration again. Agilent recommends that, once calibration is performed, you label the cables with the channel on which they were calibrated.

## Starting the DDR2(+LP) Compliance Test Application

- 1 Ensure that the RAM reliability test software is running in the computer system where the Device Under Test (DUT) is attached. This software performs tests to all unused RAM in the system by producing a repetitive burst of read-write data signals to the DDR2 memory.

- 2 To start the DDR2(+LP) Compliance Test Application: From the Infinitum oscilloscope's main menu, choose Analyze>Automated Test Apps>DDR2(+LP) Test.

| Analyze Utilities<br>Math (FFT and m<br>Histogram<br>Mask Test<br>Jitter Setup<br>Serial Data<br>Equalization<br>Apps Needing Up<br>Automated Test A<br>Vector Signal Ana | ore) 6.<br>n 4 C<br>grade DDR2 2.50 Test                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File View                                                                                                                                                                 | st DDR2(+LP) Device 1 *         Tools         Help         Image: Set Up         Set Up         Set Up         Set Up         Set Up         Device Identifier:         Image: Setting         Key in any value             Set Mask File         Derate Table File |

| Run Tests                                                                                                                                                                 | ☐ Low Power                                                                                                                                                                                                                                                         |

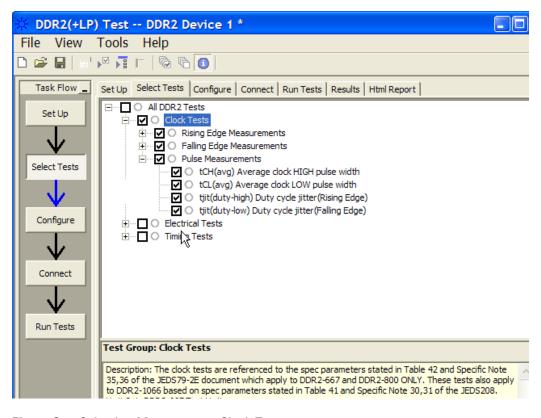

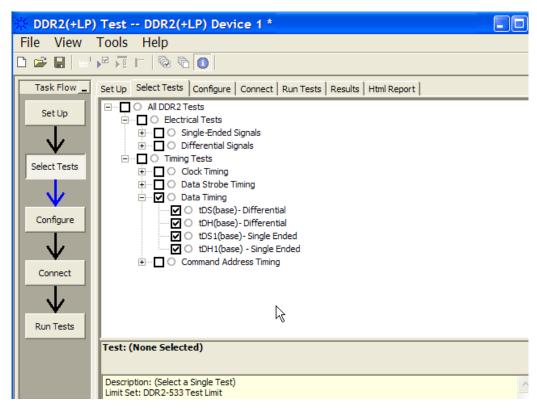

**Figure 1** The DDR2(+LP) Compliance Test Application

#### **NOTE** If DDR2(+LP) Test does not appear in the Automated Test Apps menu, the DDR2(+LP) Compliance Test Application has not been installed (see Chapter 1, "Installing the DDR2(+LP) Compliance Test Application").

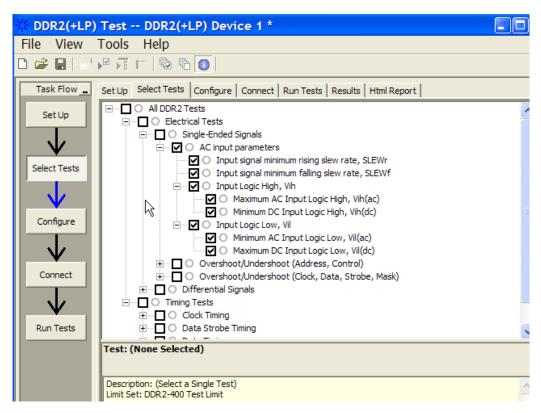

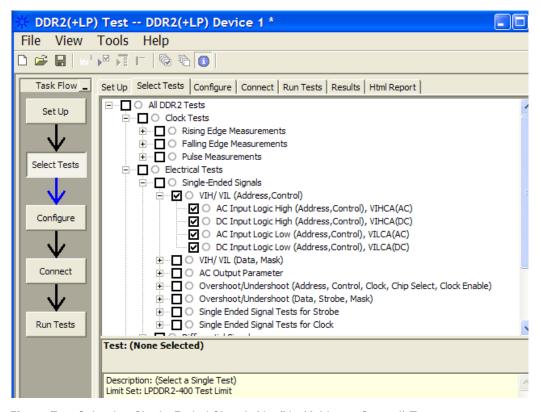

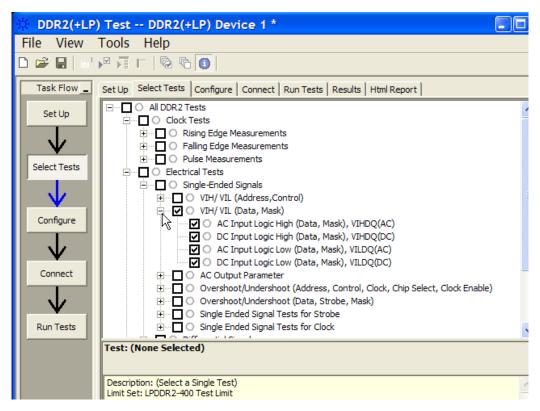

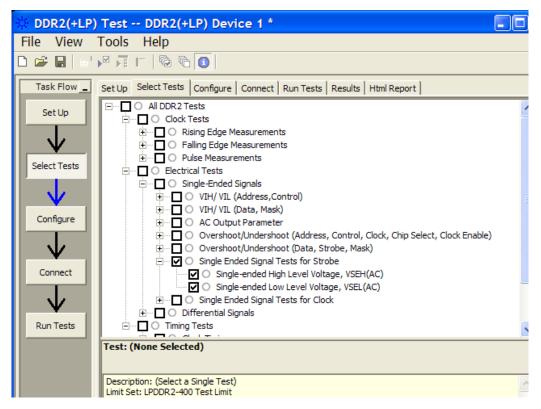

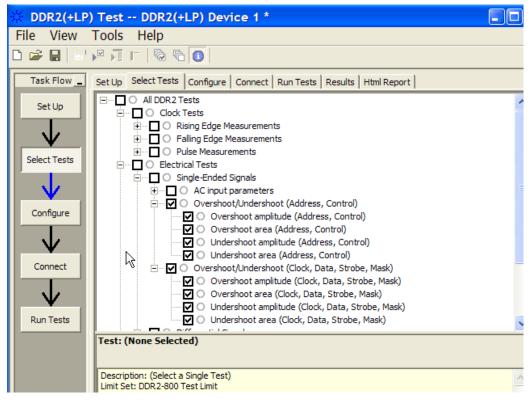

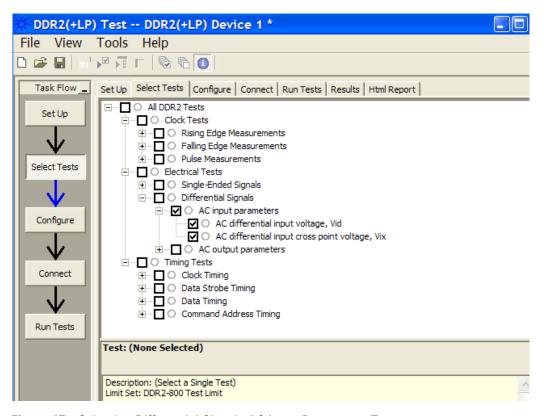

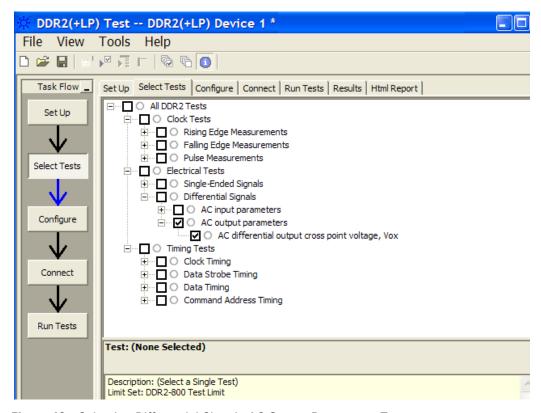

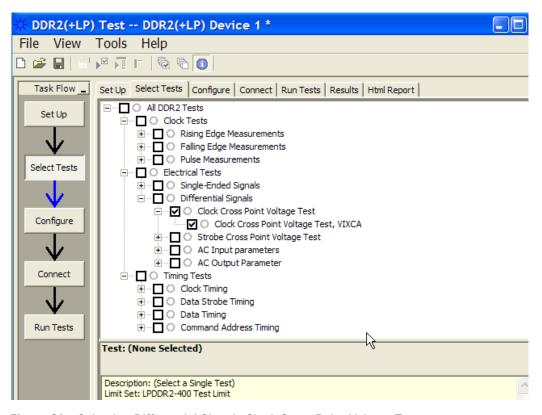

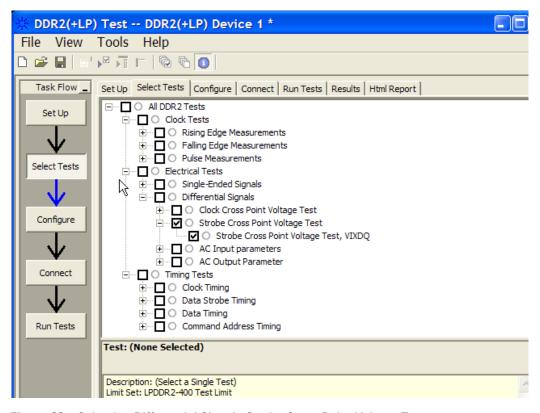

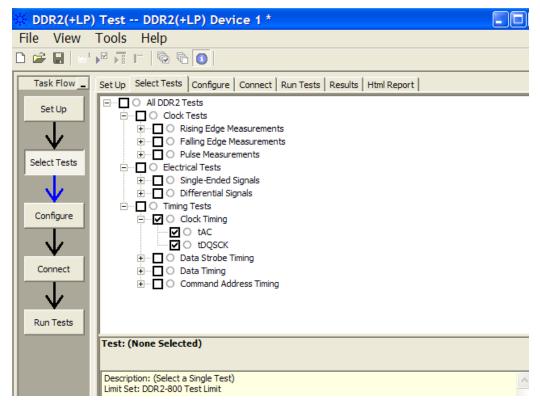

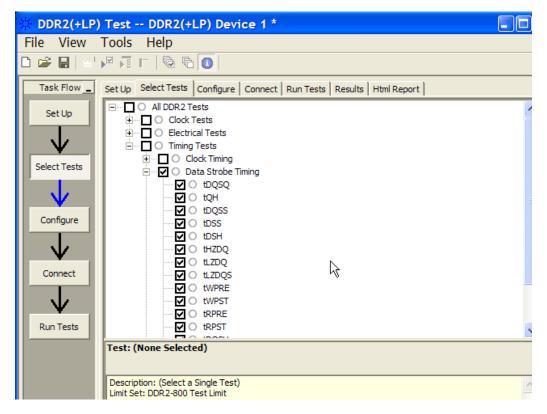

Figure 1 shows the DDR2(+LP) Compliance Test Application main window. The task flow pane, and the tabs in the main pane, show the steps you take in running the automated tests:

| Set Up       | Lets you identify and setup the test environment,<br>including information about the device under test.                                                                                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select Tests | Lets you select the tests you want to run. The tests<br>are organized hierarchically so you can select all tests<br>in a group. After tests are run, status indicators show<br>which tests have passed, failed, or not been run, and<br>there are indicators for the test groups. |

| Configure    | Lets you configure test parameters (like memory depth). This information appears in the HTML report.                                                                                                                                                                              |

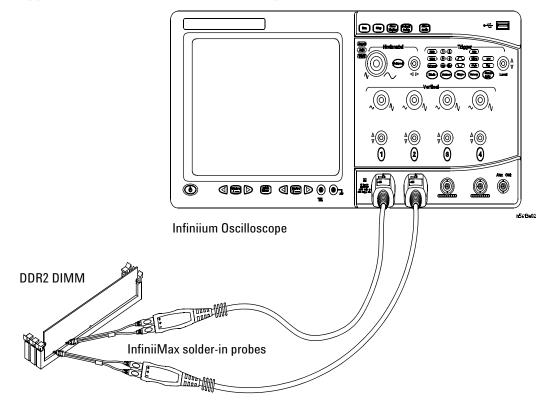

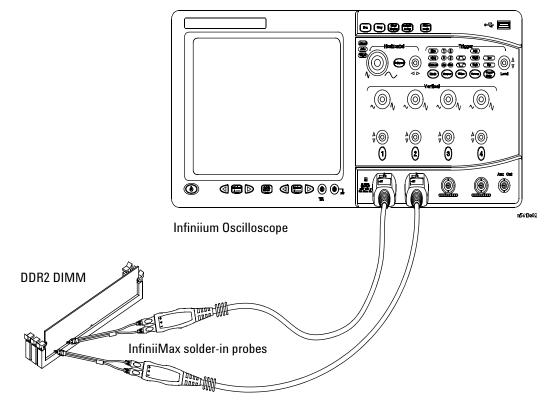

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests to be run.                                                                                                                                                                                       |

| Run Tests    | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing.        |

| Results      | Contains more detailed information about the tests<br>that have been run. You can change the thresholds at<br>which marginal or critical warnings appear.                                                                                                                         |

| Html Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                               |

#### NOTE

When you close the DDR2(+LP) application, each channel's probe is configured as single-ended or differential depending on the last DDR2(+LP) test that was run.

#### **Online Help Topics**

For information on using the DDR2(+LP) Compliance Test Application, see its online help (which you can access by choosing Help>Contents... from the application's main menu). The DDR2(+LP) Compliance Test Application's online help describes:

- Starting the DDR2(+LP) compliance test application.

- To view/minimize the task flow pane

- To view/hide the toolbar

- Creating or Opening a Test Project

- Setting up DDR2(+LP) test environment.

- Selecting tests.

- Configuring tests.

- User-Defined compliance limits.

- Connecting the oscilloscope to the DUT.

- Running tests.

- Viewing test results.

- To delete trials from the results

- · To show reference images and flash mask hits

- To change the display settings

- To change the remote settings

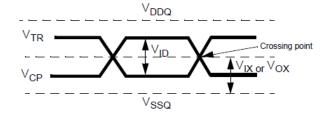

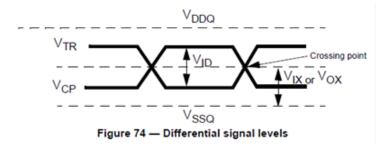

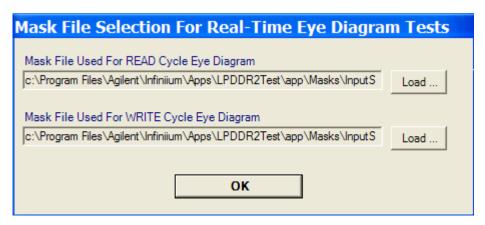

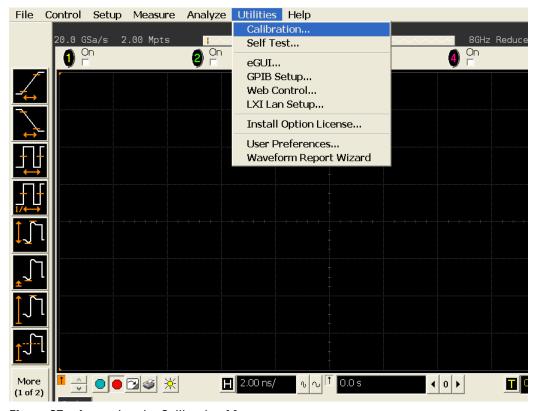

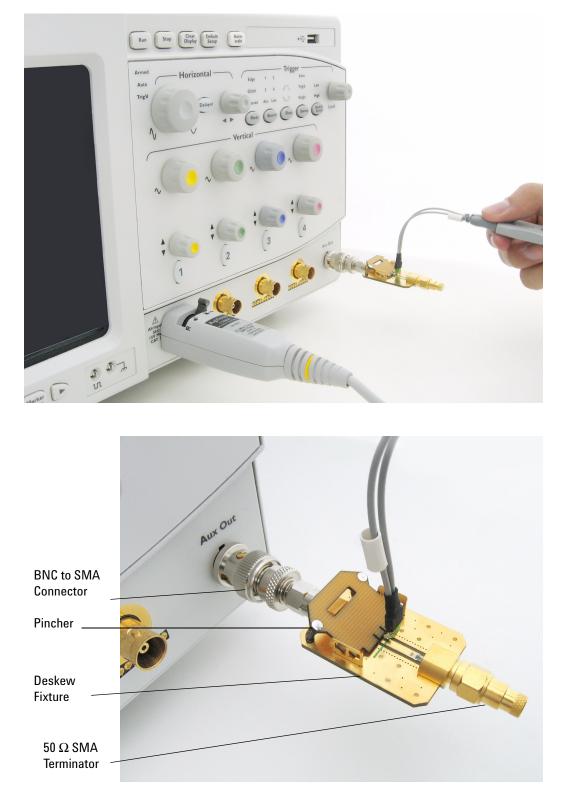

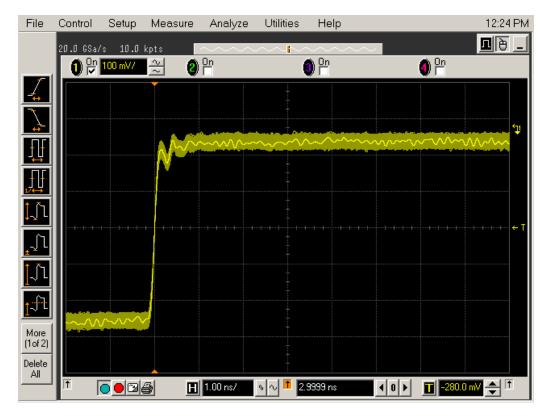

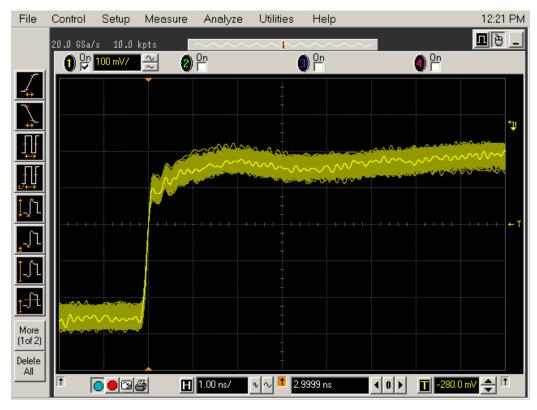

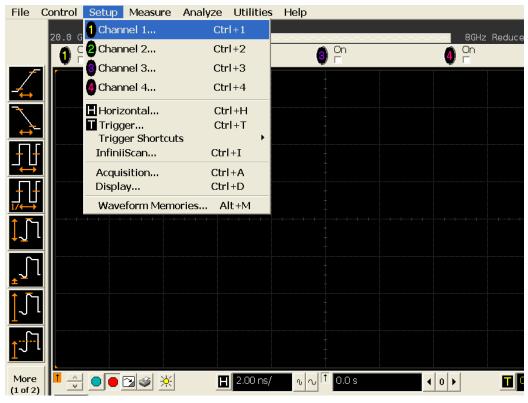

- To change the margin thresholds and trial report display